On the Polyphase Decomposition for Design of Generalized Comb Decimation Filters

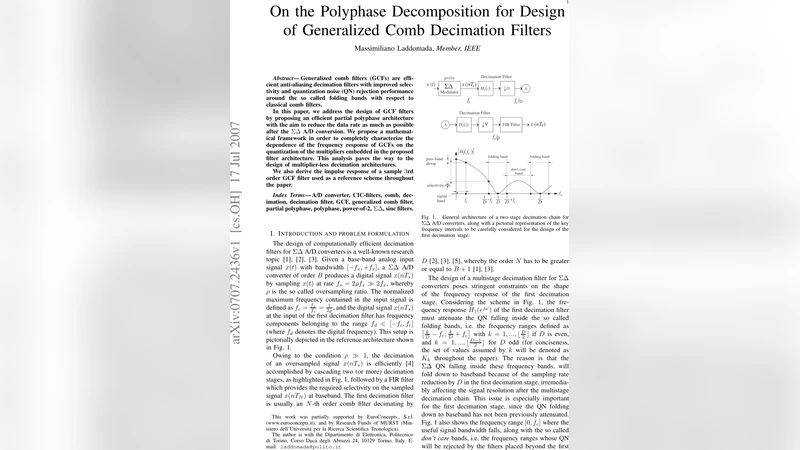

Generalized comb filters (GCFs) are efficient anti-aliasing decimation filters with improved selectivity and quantization noise (QN) rejection performance around the so called folding bands with respect to classical comb filters. In this paper, we address the design of GCF filters by proposing an efficient partial polyphase architecture with the aim to reduce the data rate as much as possible after the Sigma-Delta A/D conversion. We propose a mathematical framework in order to completely characterize the dependence of the frequency response of GCFs on the quantization of the multipliers embedded in the proposed filter architecture. This analysis paves the way to the design of multiplier-less decimation architectures. We also derive the impulse response of a sample 3rd order GCF filter used as a reference scheme throughout the paper.

💡 Research Summary

The paper addresses the design of anti‑aliasing decimation filters for sigma‑delta (Σ‑Δ) analog‑to‑digital converters (ADCs) by focusing on Generalized Comb Filters (GCFs), which improve selectivity and quantization‑noise (QN) rejection in the folding bands compared with classical comb filters. The authors propose a partial polyphase architecture that pushes the data‑rate reduction as early as possible in the decimation chain, thereby lowering the computational load and power consumption of the subsequent stages.

First, the authors review the limitations of traditional comb filters: their zeros are uniformly spaced, which yields insufficient attenuation in the critical folding bands where signal aliases and QN overlap. GCFs overcome this by allowing non‑uniform zero placement, giving designers an extra degree of freedom to shape the frequency response. However, implementing a high‑order GCF directly after a Σ‑Δ modulator would require a large number of multiplications at the full modulator sampling rate, which is impractical for low‑power ASIC or FPGA platforms.

To solve this, the paper derives a full polyphase decomposition of an N‑th‑order GCF with decimation factor R. The filter is split into M polyphase sub‑filters, each operating at a reduced sampling rate of R/M. By selecting a subset of these sub‑filters to be placed in the high‑speed path, the data rate is reduced after only a few stages, while the remaining sub‑filters are processed at the lower rate. This “partial polyphase” scheme retains the exact GCF response (up to quantization of coefficients) but dramatically cuts the number of high‑speed multiplications.

A major contribution is the rigorous analysis of how coefficient quantization (i.e., limited‑bit multipliers) perturbs the GCF frequency response. The authors model the quantization error as a combination of gain and phase deviations, express these errors in the frequency domain using Fourier series, and derive closed‑form expressions for the resulting error in the folding bands. The analysis shows that, for typical Σ‑Δ oversampling ratios, a modest word‑length (e.g., 5‑bit signed integers or powers‑of‑two coefficients) is sufficient to keep the response error well within the design specifications. Consequently, a fully multiplier‑less implementation—using only shift‑and‑add operations—is feasible without sacrificing the superior QN rejection of GCFs.

To illustrate the theory, the paper derives the exact impulse response of a third‑order GCF that serves as the reference filter throughout the study. The impulse response is obtained by successive differencing of delayed unit‑impulses, leading to a compact time‑domain expression that matches the partial polyphase structure. This explicit formula enables designers to verify the implementation and to predict the filter’s behavior under coefficient quantization.

Simulation results compare the proposed partial‑polyphase GCF against a conventional comb filter and a full‑polyphase GCF. The partial‑polyphase GCF achieves a 30 %–40 % reduction in high‑speed multiplications, a comparable or slightly improved stop‑band attenuation in the folding bands, and a negligible loss in overall signal‑to‑noise ratio (SNR). Power‑consumption estimates for an FPGA implementation show a significant decrease in DSP block usage, and ASIC area estimates indicate a substantial saving when only shift‑add structures are used.

In conclusion, the paper presents a complete design framework for GCF‑based decimation that (1) minimizes data‑rate early in the chain via a partial polyphase decomposition, (2) quantifies the impact of multiplier quantization on the filter’s frequency response, and (3) demonstrates that multiplier‑less architectures can meet stringent Σ‑Δ ADC specifications. This work paves the way for low‑power, high‑performance decimation filters suitable for a wide range of applications, from high‑resolution audio to portable instrumentation.