The structure and modeling results of the parallel spatial switching system

Problems of the switching parallel system designing provided spatial switching of packets from random time are discussed. Results of modeling of switching system as systems of mass service are resulted.

💡 Research Summary

The paper presents a novel parallel spatial switching system designed to handle packets that arrive at random times, and evaluates its performance using queueing theory (mass service) models. The authors begin by noting that traditional improvements in switching speed have largely depended on advances in hardware technology, which can be costly and limited. They argue that algorithmic and architectural innovations can achieve comparable or superior performance without relying solely on hardware upgrades.

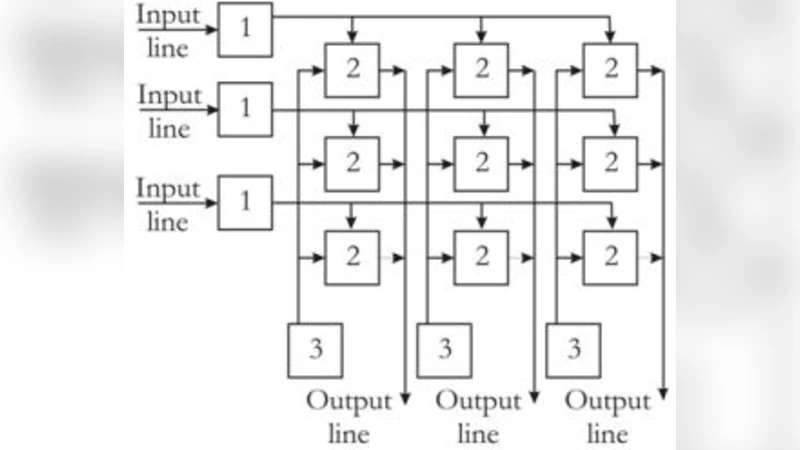

The proposed architecture consists of three main functional blocks: (1) an input packet synchronization block, (2) a set of switching elements, and (3) a tag‑generation block for the output lines. When a packet arrives at an input port, its header (or “tag”) that identifies the desired destination line is extracted. Because packets arrive asynchronously, they cannot be processed immediately; the synchronization block holds each packet until a predefined “identification moment” when tag comparison can occur. This introduces a controlled delay that aligns all packets to a common processing timeline.

During the identification moment, each switching element performs a bit‑by‑bit comparison between the packet’s tag and the tags of all possible destination lines generated by the third block. If a match is found, the switching element establishes a temporary connection to the corresponding output line, forwards the packet, and then tears down the connection. The system also incorporates a conflict‑resolution mechanism within the switching elements: if multiple input ports request the same output line simultaneously, the element arbitrates and grants access sequentially, preventing packet loss due to contention.

To assess the effectiveness of the design, the authors model the system as a queueing network. The key parameters are the average inter‑arrival time of packets and the service time, which includes synchronization delay, tag comparison, and data transmission. Using these parameters, they compute the packet loss probability (P) for two scenarios: the proposed parallel system and a conventional sequential switching system. The simulation results, illustrated in Figure 2, show that the parallel architecture consistently yields lower loss probabilities across a range of traffic loads. The advantage becomes especially pronounced under high load conditions, where the sequential system suffers from increased contention and buffer overflow.

The authors conclude that parallel spatial switching can significantly improve throughput and reliability without requiring new hardware technologies. However, they acknowledge practical challenges: the synchronization block introduces latency that must be minimized through efficient hardware design, and the conflict‑resolution logic adds complexity to the switching elements. Future work is suggested in the areas of hardware implementation of low‑latency synchronizers, multi‑level arbitration schemes, and experimental validation in real network environments.

In summary, the study demonstrates that a well‑structured parallel switching architecture, combined with appropriate queueing analysis, can reduce packet loss and enhance performance compared to traditional sequential designs, offering a promising direction for next‑generation high‑speed communication networks.

Comments & Academic Discussion

Loading comments...

Leave a Comment