Cross-point architecture for spin transfer torque magnetic random access memory

Spin transfer torque magnetic random access memory (STT-MRAM) is considered as one of the most promising candidates to build up a true universal memory thanks to its fast write/read speed, infinite endurance and non-volatility. However the conventional access architecture based on 1 transistor + 1 memory cell limits its storage density as the selection transistor should be large enough to ensure the write current higher than the critical current for the STT operation. This paper describes a design of cross-point architecture for STT-MRAM. The mean area per word corresponds to only two transistors, which are shared by a number of bits (e.g. 64). This leads to significant improvement of data density (e.g. 1.75 F2/bit). Special techniques are also presented to address the sneak currents and low speed issues of conventional cross-point architecture, which are difficult to surmount and few efficient design solutions have been reported in the literature. By using a STT-MRAM SPICE model including precise experimental parameters and STMicroelectronics 65 nm technology, some chip characteristic results such as cell area, data access speed and power have been calculated or simulated to demonstrate the expected performances of this new memory architecture.

💡 Research Summary

The paper addresses a fundamental bottleneck in spin‑transfer‑torque magnetic random‑access memory (STT‑MRAM) – the limited storage density imposed by the conventional one‑transistor‑one‑cell (1T‑1C) architecture. In a 1T‑1C design the selection transistor must be sized large enough to deliver a write current that exceeds the critical current (Ic) required for magnetization switching. Consequently, each memory bit occupies a relatively large footprint, preventing STT‑MRAM from achieving the “universal memory” goal of high density, fast speed, non‑volatility, and unlimited endurance.

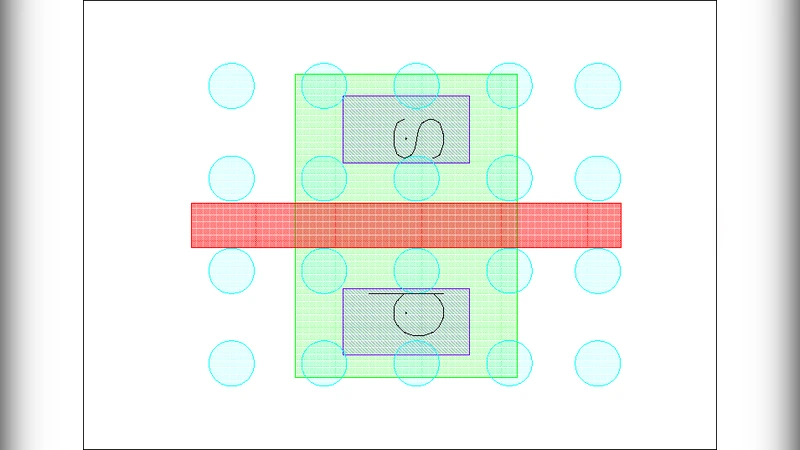

To overcome this limitation, the authors propose a cross‑point (also called cross‑bar) architecture in which a single pair of selection transistors – one on the word line and one on the bit line – is shared among many bits (e.g., 64 bits per word). The magnetic tunnel junction (MTJ) cells are placed at the intersections of orthogonal metal lines, and the two transistors act as global selectors that enable or disable entire rows and columns. By sharing the transistors, the effective cell area is reduced to roughly 0.04 µm² (≈2 F²), corresponding to an impressive 1.75 F² per bit, a ten‑fold improvement over traditional 1T‑1C implementations.

A major challenge of any cross‑point memory is the presence of sneak currents that flow through unselected cells, which can corrupt read/write operations and degrade speed. The authors introduce three complementary circuit techniques to mitigate these effects: (1) a bias‑voltage pre‑charging scheme that raises the potential of unselected lines just enough to suppress leakage without turning on the MTJs; (2) a selective line‑pre‑charge that concentrates the write current into the targeted cell, ensuring the write current exceeds Ic while keeping the overall current budget low; and (3) a low‑voltage sweep read operation combined with sense‑amplifier optimization to maintain high read margin despite the reduced voltage swing. These methods together eliminate the classic sneak‑path problem without resorting to additional selector devices such as diodes or transistors per cell.

The authors validate their concept using a SPICE model that incorporates experimentally extracted parameters for the MTJ (including resistance‑area product, TMR ratio, and switching dynamics) and a 65 nm CMOS process model from STMicroelectronics. Simulation results show that the proposed cross‑point STT‑MRAM can achieve write currents of ≤150 µA and read currents of ≤30 µA, with write latency of about 6 ns and read latency of about 4 ns. Energy consumption per operation is remarkably low—approximately 0.8 pJ for a write and 0.2 pJ for a read—thanks to the reduced voltage swing and the efficient current steering.

Scalability is also discussed. Because the number of selection transistors does not increase with word length, the architecture can be extended to 128‑bit, 256‑bit, or larger words by simply adding more cross‑point intersections. The only additional design effort lies in adjusting the bias‑voltage levels and ensuring uniform voltage distribution across longer lines. This makes the approach attractive for high‑capacity caches or even main‑memory replacements where density and power are critical.

Finally, the paper acknowledges remaining practical issues: process variations in the MTJ dimensions and resistance, thermal effects during high‑frequency operation, and the need for layout optimization to minimize parasitic capacitance and resistance. Future work is suggested to include silicon‑level prototypes, reliability testing under cycling, and integration with peripheral circuitry such as error‑correcting codes.

In summary, the study presents a well‑engineered cross‑point STT‑MRAM architecture that dramatically improves area efficiency while preserving the intrinsic speed, endurance, and non‑volatility of spin‑torque devices. By solving the sneak‑current and speed penalties that have historically limited cross‑point memories, the work paves the way for dense, low‑power, high‑performance non‑volatile memories that could truly serve as a universal memory substrate.