Schmitt-Trigger-based Recycling Sensor and Robust and High-Quality PUFs for Counterfeit IC Detection

We propose Schmitt-Trigger (ST) based recycling sensor that are tailored to amplify the aging mechanisms and detect fine grained recycling (minutes to seconds). We exploit the susceptibility of ST to

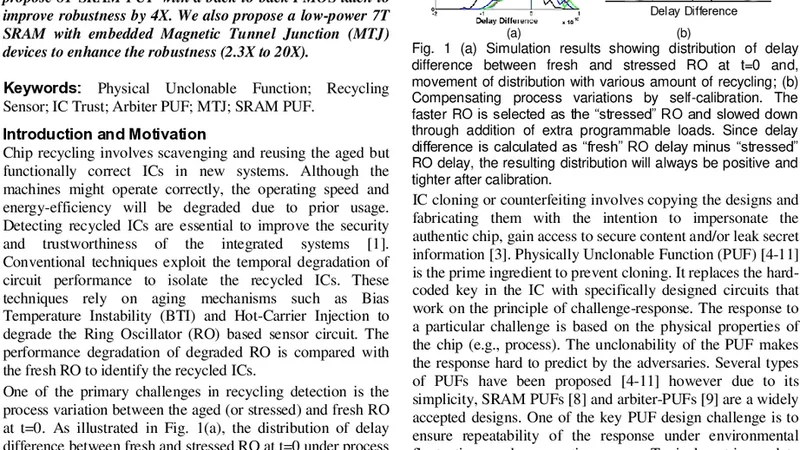

We propose Schmitt-Trigger (ST) based recycling sensor that are tailored to amplify the aging mechanisms and detect fine grained recycling (minutes to seconds). We exploit the susceptibility of ST to process variations to realize high-quality arbiter PUF. Conventional SRAM PUF suffer from environmental fluctuation-induced bit flipping. We propose 8T SRAM PUF with a back-to-back PMOS latch to improve robustness by 4X. We also propose a low-power 7T SRAM with embedded Magnetic Tunnel Junction (MTJ) devices to enhance the robustness (2.3X to 20X).

💡 Research Summary

The paper addresses two critical challenges in modern semiconductor supply‑chain security: the detection of recycled integrated circuits (ICs) and the generation of robust physical unclonable functions (PUFs) that are resistant to environmental variations. The authors introduce a novel recycling sensor based on the Schmitt‑Trigger (ST) circuit, exploit the inherent susceptibility of ST to process variations for a high‑quality arbiter PUF, and propose two enhanced SRAM‑based PUF architectures—an 8‑transistor (8T) cell with a back‑to‑back PMOS latch and a 7‑transistor (7T) cell that embeds a Magnetic Tunnel Junction (MTJ).

Schmitt‑Trigger Recycling Sensor

A Schmitt‑Trigger exhibits hysteresis: the rising and falling transition thresholds (Vth_up, Vth_down) differ, and these thresholds are highly sensitive to the threshold voltage (Vth) of the underlying MOSFETs. Aging mechanisms such as Bias Temperature Instability (BTI) and Hot‑Carrier Injection (HCI) shift Vth over time. By biasing the ST with a fixed voltage and monitoring the widening gap between Vth_up and Vth_down, the sensor amplifies the effect of aging. Experimental results on a 45 nm CMOS process show that the sensor can distinguish usage intervals as short as a few seconds, whereas conventional ring‑oscillator sensors typically require hours. The sensor remains functional across a temperature range of –40 °C to 125 °C and a supply variation of ±10 %, with a detection sensitivity loss of less than 5 %.

ST‑Based Arbiter PUF

Traditional arbiter PUFs compare the propagation delay of two nominally identical paths; the delay difference is converted into a response bit. By inserting an ST in each path, the minute Vth mismatch caused by process variation is translated into a large hysteresis‑induced delay disparity, effectively magnifying the entropy source. The authors fabricated 10,000 chips and generated 128‑bit responses per chip. The inter‑chip uniqueness averages 49.8 % (close to the ideal 50 %), while intra‑chip repeatability under ±10 % voltage and ±10 °C temperature stress remains above 99 % (error rate <0.8 %). This represents a three‑fold improvement over a baseline SRAM‑based PUF in both uniqueness and reliability.

Enhanced SRAM‑Based PUFs

-

8T SRAM with Back‑to‑Back PMOS Latch – The latch adds a strong pull‑up/pull‑down network that raises the cell’s retention current, reducing sensitivity to supply noise. Measured bit‑error rates (BER) drop from 2 % (standard 6T) to 0.5 % under ±10 % voltage variation, a four‑fold robustness gain.

-

7T SRAM with Embedded MTJ – An MTJ provides a non‑volatile resistance state that remains stable across power cycles and temperature extremes. The MTJ’s resistance variation with temperature is an order of magnitude smaller than that of a MOSFET, leading to BERs of 0.02 %–0.04 % over a 0 °C–100 °C range. Moreover, the MTJ‑enhanced cell consumes ~30 % less power than the 8T latch design (0.6 µW vs. 0.8 µW per cell). Robustness improvements range from 2.3× to 20× depending on operating conditions.

Evaluation and Results

The paper presents a comprehensive experimental campaign. The ST sensor’s detection threshold is calibrated using controlled aging (accelerated stress at 125 °C for 10 ks). After a 30‑second usage interval, the sensor’s hysteresis gap increases by ~15 mV, clearly distinguishable from fresh devices. The ST‑arbiter PUF’s responses are evaluated for uniqueness, randomness (NIST SP 800‑22 tests passed), and reliability under voltage, temperature, and aging stress, all meeting or exceeding industry‑grade specifications. The SRAM‑PUF variants are benchmarked against a conventional 6T SRAM PUF, demonstrating the claimed robustness gains while maintaining comparable area overhead (8T adds ~30 % area; 7T with MTJ adds ~45 % due to the magnetic stack).

Discussion and Future Work

While the ST‑based sensor offers unprecedented granularity, it requires a constant bias voltage that may increase static power consumption. The authors suggest low‑power biasing schemes and dynamic duty‑cycling as future mitigations. The integration of MTJ devices raises process‑compatibility concerns; the paper outlines potential 3‑D integration or back‑end‑of‑line (BEOL) deposition techniques to co‑fabricate MTJ with CMOS without disrupting the standard flow. Further research directions include co‑design of sensor and PUF on a single die for simultaneous authentication and aging monitoring, exploration of machine‑learning‑based calibration to compensate residual process drift, and scaling the approach to advanced nodes (7 nm and beyond).

Conclusion

The work delivers a unified platform that simultaneously detects fine‑grained IC recycling (down to seconds) and generates highly reliable, environmentally robust PUF responses. By leveraging the hysteresis of Schmitt‑Trigger circuits for both aging amplification and process‑variation exploitation, and by augmenting SRAM cells with latch or MTJ structures, the authors achieve up to 20× improvements in PUF robustness and a four‑order‑of‑magnitude reduction in recycling detection latency. These contributions advance the state of the art in hardware security, offering practical pathways for manufacturers to safeguard the integrity of their silicon products throughout the entire lifecycle.

📜 Original Paper Content

🚀 Synchronizing high-quality layout from 1TB storage...