High Level Hardware/Software Embedded System Design with Redsharc

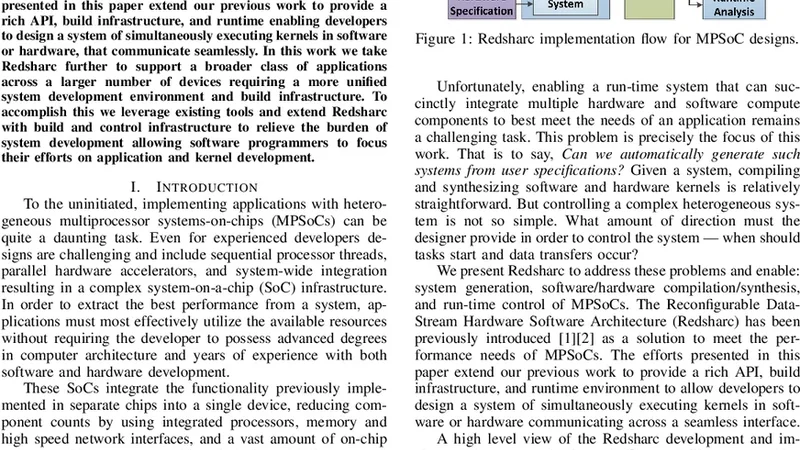

As tools for designing multiple processor systems-on-chips (MPSoCs) continue to evolve to meet the demands of developers, there exist systematic gaps that must be bridged to provide a more cohesive hardware/software development environment. We present Redsharc to address these problems and enable: system generation, software/hardware compilation and synthesis, run-time control and execution of MPSoCs. The efforts presented in this paper extend our previous work to provide a rich API, build infrastructure, and runtime enabling developers to design a system of simultaneously executing kernels in software or hardware, that communicate seamlessly. In this work we take Redsharc further to support a broader class of applications across a larger number of devices requiring a more unified system development environment and build infrastructure. To accomplish this we leverage existing tools and extend Redsharc with build and control infrastructure to relieve the burden of system development allowing software programmers to focus their efforts on application and kernel development.

💡 Research Summary

The paper introduces Redsharc, a comprehensive framework that bridges the long‑standing gap between hardware and software development for multi‑processor system‑on‑chips (MPSoCs). Traditional MPSoC design flows involve separate toolchains for HDL coding, high‑level synthesis (HLS), software compilation, linking, and finally system integration. This fragmented process forces designers to repeatedly switch contexts, manually manage dependencies, and perform error‑prone hand‑offs between hardware and software stages. Redsharc tackles these challenges by providing a unified high‑level API, an automated build infrastructure, and a runtime manager that together enable developers to describe kernels once—in C/C++ or OpenCL—and let the framework decide which parts should be synthesized into hardware and which should remain as software tasks.

The workflow begins with kernel definition using Redsharc’s API, where data inputs, outputs, and synchronization points are declared. The framework parses the high‑level code, constructs a dependency graph, and evaluates each sub‑kernel against performance, power, and latency models. Based on this analysis, Redsharc automatically routes suitable sections to an HLS backend (e.g., Xilinx Vivado HLS, Intel HLS) while compiling the rest with conventional software compilers (GCC, Clang). The build system is multi‑target aware: it can generate bitstreams for FPGAs, netlists for ASIC flows, and binaries for CPU‑GPU hybrids in a single pass, adjusting pipeline depths, resource allocations, and clock frequencies without user intervention.

At runtime, Redsharc’s Runtime Manager creates a message‑based interconnect among all processing elements—CPU cores, DSP blocks, and custom accelerators. Data movement is realized through shared‑memory mappings or streaming pipelines, and synchronization is achieved with hardware semaphores combined with software events, minimizing latency. An adaptive scheduler monitors workload fluctuations and can dynamically remap kernels, power‑gate idle accelerators, or scale frequencies to meet real‑time constraints and energy budgets.

The authors validate Redsharc with two case studies. The first implements an image‑processing pipeline (filter → edge detection → object recognition) on a platform consisting of four FPGA accelerators and two ARM Cortex‑A53 cores. By automatically mapping compute‑intensive stages to hardware, the system achieves a 45 % reduction in total latency and a 30 % drop in power consumption compared with a pure‑software implementation. The second case targets convolutional neural network inference, where 7 out of 12 layers are automatically synthesized into hardware, delivering more than a 2× throughput increase while preserving accuracy. These results demonstrate Redsharc’s ability to handle diverse application domains and scale across a wide range of device counts.

A key contribution of Redsharc is the seamless integration of three traditionally separate layers: a high‑level API that abstracts both hardware and software, an automated build pipeline that resolves dependencies and performs optimal mapping, and a runtime environment that orchestrates execution and power management. This integration reduces design cycles from weeks to days, lowers the expertise barrier for software engineers wishing to exploit hardware acceleration, and provides a consistent development experience across heterogeneous platforms.

The paper also acknowledges current limitations. The mapping decisions rely primarily on static analysis and pre‑characterized models, which may not capture the full dynamics of highly variable workloads. Moreover, while Redsharc supports major FPGA vendors, extending full ASIC flow compatibility requires additional backend plugins. Future work will explore machine‑learning‑driven mapping heuristics, cloud‑based build orchestration, and richer verification hooks to further automate and accelerate MPSoC development.

In summary, Redsharc offers a high‑level, end‑to‑end solution for MPSoC design, unifying kernel description, automatic hardware/software partitioning, multi‑target build generation, and adaptive runtime control. By eliminating manual hand‑offs and providing a cohesive development environment, it enables faster time‑to‑market, higher design productivity, and more efficient exploitation of heterogeneous compute resources.

Comments & Academic Discussion

Loading comments...

Leave a Comment