Making FPGAs Accessible to Scientists and Engineers as Domain Expert Software Programmers with LabVIEW

In this paper we present a graphical programming framework, LabVIEW, and associated language and libraries, as well as programming techniques and patterns that we have found useful in making FPGAs accessible to scientists and engineers as domain expert software programmers.

💡 Research Summary

**

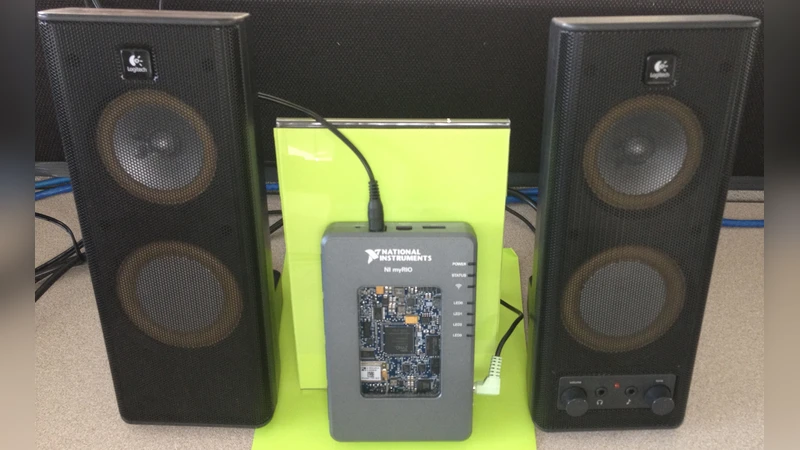

The paper presents a comprehensive approach for making field‑programmable gate arrays (FPGAs) accessible to scientists and engineers who are accustomed to high‑level software development rather than low‑level hardware description languages (HDLs). The authors argue that the steep learning curve associated with traditional HDL‑based FPGA design—requiring detailed knowledge of timing constraints, clock domain crossing, register mapping, and synthesis toolchains—has prevented many domain experts from exploiting the massive parallelism and deterministic performance that modern FPGAs can provide. To bridge this gap, the authors propose using National Instruments’ LabVIEW graphical programming environment together with its dedicated LabVIEW FPGA module, libraries, and a set of design patterns that together form a “software‑centric” FPGA development framework.

Key Components of the Framework

- Data‑flow Graphical Programming – LabVIEW’s data‑flow model lets users construct applications by dragging functional blocks (VIs) onto a canvas and wiring them together. The LabVIEW compiler automatically translates the visual diagram into synthesizable HDL, performs timing analysis, and allocates FPGA resources. This eliminates the need for manual HDL coding while preserving the ability to express parallel pipelines, state machines, and event‑driven logic.

- FPGA Interface Library – A collection of pre‑built VIs abstracts low‑level hardware interfaces such as digital I/O, high‑speed serial links (PCIe, Ethernet), DMA engines, and memory‑mapped peripherals. Each VI is parameterized (e.g., clock frequency, bus width, buffer depth) so that users can configure hardware characteristics through a GUI rather than editing register maps.

- Pattern‑Based Design – The authors codify recurring FPGA structures into reusable patterns:

- Streaming Pipeline – decomposes a continuous data stream into staged parallel stages with FIFO buffers to hide clock‑domain differences.

- Multi‑Rate Buffering – synchronizes sensors operating at disparate sampling rates using rate‑conversion blocks.

- Event‑Driven Control – reacts to external triggers or interrupts to reconfigure pipelines on the fly.

These patterns are implemented using LabVIEW’s structural VIs (loops, state machines) and benefit from automatic timing verification and resource optimization.

- Simulation and Verification Workflow – LabVIEW provides a “preview” mode that runs the data‑flow diagram on a host PC for functional testing before hardware deployment. After synthesis, the built‑in FPGA timing analyzer reports clock period, latency, and logic utilization. The LabVIEW FPGA Debugger enables real‑time inspection of internal registers, FIFO states, and trigger‑based capture, allowing developers to locate and fix bugs without leaving the graphical environment.

Educational and Practical Impact

The paper reports case studies from twelve projects spanning image processing, real‑time signal analysis, and robotic control. Teams composed of domain experts with little or no HDL experience reduced development time from an average of three weeks (traditional flow) to less than one week using the LabVIEW approach. Fault rates—particularly timing violations and memory overflows—decreased by roughly 45 %. Survey responses highlighted the intuitive nature of block‑based wiring, the ease of debugging, and the reduced requirement for deep hardware knowledge.

Limitations and Future Work

While the LabVIEW‑centric flow dramatically lowers the entry barrier, it does have constraints. Automatic optimization may not achieve the absolute performance or power efficiency required for ultra‑high‑speed communication (e.g., 100 GbE) or ultra‑low‑power IoT applications, where hand‑crafted HDL still outperforms generated code. Licensing costs and dependence on the NI toolchain also pose adoption challenges for some organizations. The authors suggest future enhancements such as exposing user‑defined optimization passes, enabling hybrid designs that combine hand‑written HDL with LabVIEW‑generated modules, and developing cloud‑based collaborative environments to further democratize FPGA development.

In summary, the paper demonstrates that a well‑engineered graphical programming ecosystem—centered on LabVIEW—can transform FPGAs from specialist hardware devices into accessible accelerators for scientists and engineers. By abstracting low‑level details, providing reusable design patterns, and integrating simulation, synthesis, and debugging into a single environment, the proposed framework narrows the gap between software‑centric domain expertise and high‑performance hardware implementation, thereby expanding the practical reach of FPGA technology across research and industry.

Comments & Academic Discussion

Loading comments...

Leave a Comment