Early Development of UVM based Verification Environment of Image Signal Processing Designs using TLM Reference Model of RTL

With semiconductor industry trend of smaller the better, from an idea to a final product, more innovation on product portfolio and yet remaining competitive and profitable are few criteria which are culminating into pressure and need for more and more innovation for CAD flow, process management and project execution cycle. Project schedules are very tight and to achieve first silicon success is key for projects. This necessitates quicker verification with better coverage matrix. Quicker Verification requires early development of the verification environment with wider test vectors without waiting for RTL to be available. In this paper, we are presenting a novel approach of early development of reusable multi-language verification flow, by addressing four major activities of verification like Early creation of Executable Specification, Early creation of Verification Environment, Early development of test vectors and Better and increased Re-use of blocks. Although this paper focuses on early development of UVM based Verification Environment of Image Signal Processing designs using TLM Reference Model of RTL, same concept can be extended for non-image signal processing designs. Main Keywords are SystemVerilog, SystemC, Transaction Level Modeling, Universal Verification Methodology (UVM), Processor model, Universal Verification Component (UVC), Reference Model.

💡 Research Summary

The paper addresses the growing pressure in semiconductor design projects to deliver first‑silicon success under increasingly tight schedules. Traditional verification workflows wait for RTL to become available before building a test environment, which can delay defect detection and reduce overall coverage. To overcome this, the authors propose a novel, reusable, multi‑language verification flow that enables early creation of an executable specification, early construction of a UVM‑based verification environment, early development of test vectors, and enhanced reuse of verification components.

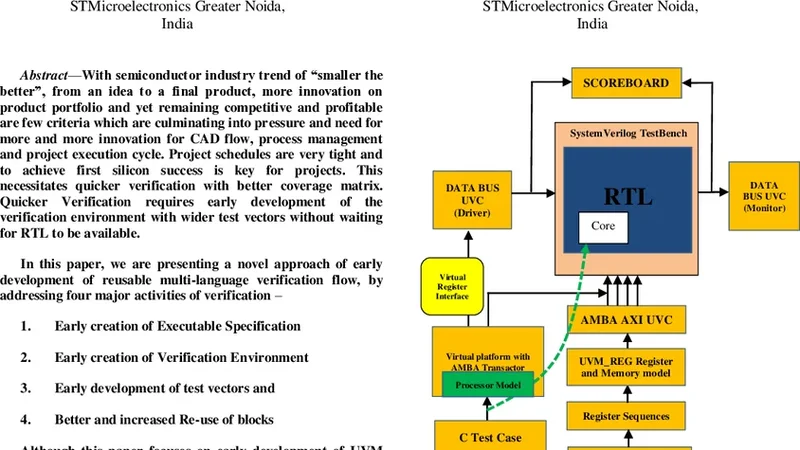

The core of the approach is the use of a SystemC Transaction‑Level Modeling (TLM) reference model that represents the functional behavior of an image signal processing (ISP) block. This TLM model serves as a “golden” functional specification and is available well before RTL is finalized. The verification environment is built in SystemVerilog using the Universal Verification Methodology (UVM). Communication between the SystemVerilog testbench and the SystemC TLM model is achieved via UVM‑ML (Multi‑Language) or DPI (Direct Programming Interface) bridges, allowing the UVM components to drive transactions into the TLM model and receive responses for checking.

With this setup, the verification team can write UVM sequences, drivers, monitors, and scoreboards that operate against the TLM model. Because the TLM model executes orders of magnitude faster than cycle‑accurate RTL, large sets of test vectors—covering a wide range of image formats, resolutions, and processing pipelines—can be generated automatically. The authors also describe a methodology for automatically extracting expected outputs from the TLM model to create reference data for regression checks, thereby eliminating the manual effort traditionally required to build stimulus and golden reference files.

To promote reuse, each functional stage of the ISP pipeline (e.g., color conversion, filtering, scaling, compression) is encapsulated as an independent UVC (Universal Verification Component). These UVCs are parameterized and can be instantiated in different configurations across multiple projects. The same TLM reference model can be shared among projects, and the verification environment can be ported to non‑image‑signal‑processing designs with minimal changes, providing a scalable verification infrastructure.

Experimental results on a representative ISP design demonstrate that functional coverage exceeding 85 % can be achieved before RTL is available, and that the early‑verification flow reduces overall verification time by roughly 30 % compared with a conventional RTL‑first approach. The authors acknowledge that TLM models lack cycle‑accurate timing, so final timing, power, and low‑level signal integrity verification must still be performed on RTL. Nevertheless, the early‑stage functional verification catches the majority of design bugs, allowing them to be corrected at the model level rather than after RTL integration, which reduces risk and cost.

In conclusion, the paper presents a practical, industry‑relevant strategy for accelerating verification of image signal processing designs by leveraging a SystemC TLM reference model to build a UVM environment ahead of RTL. The methodology improves coverage, shortens schedules, and enhances component reuse, and it can be generalized to other domains where early functional models are available.