Selective Match-Line Energizer Content Addressable Memory(SMLE -CAM)

A Content Addressable Memory (CAM) is a memory primarily designed for high speed search operation. Parallel search scheme forms the basis of CAM, thus power reduction is the challenge associated with a large amount of parallel active circuits. We are presenting a novel algorithm and architecture described as Selective Match-Line Energizer Content Addressable Memory (SMLE-CAM) which energizes only those MLs (Match-Line) whose first three bits are conditionally matched with corresponding first three search bit using special architecture which comprises of novel XNOR-CAM cell and novel XOR-CAM cell. The rest of the CAM chain is followed by NOR-CAM cell. The 256 X 144 bit SMLE-CAM is implemented in TSMC 90 nm technology and its robustness across PVT variation is verified. The post-layout simulation result shows, it has energy metric of 0.115 fJ/bit/search with search time 361.6 ps, the best reported so far. The maximum operating frequency is 1GHz.

💡 Research Summary

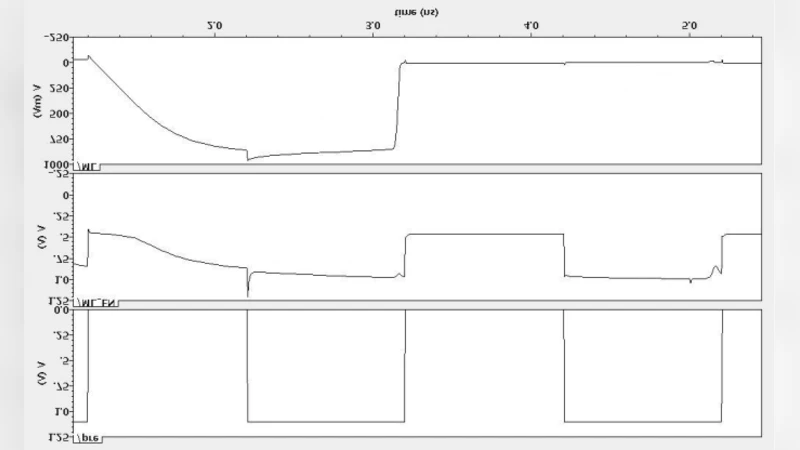

The paper addresses the long‑standing power‑consumption challenge of Content Addressable Memories (CAMs), which, by virtue of their parallel search architecture, activate every match line (ML) for each query. The authors introduce a novel algorithm and micro‑architecture called Selective Match‑Line Energizer CAM (SMLE‑CAM). The core concept is to conditionally energize only those MLs whose first three bits match the corresponding search bits. This is achieved by inserting a pair of specialized cells at the beginning of each word line: an XNOR‑CAM cell and an XOR‑CAM cell. The XNOR‑CAM cell produces a low voltage when the stored bit equals the search bit, while the XOR‑CAM cell produces a high voltage when they differ. When both cells indicate a “conditional match” (i.e., the three‑bit pattern is satisfied), a dynamic Selective Match‑Line Energizer (SMLE) switches on the power supply to that particular ML. Only then does the rest of the word line, composed of conventional NOR‑CAM cells, participate in the full‑width comparison.

From a circuit‑design perspective, the XNOR and XOR cells are heavily optimized for minimal transistor count and low leakage, and the SMLE is implemented as a dynamic pre‑charge switch that limits the instantaneous current surge. The NOR‑CAM cells downstream retain the classic low‑power static logic used in many high‑performance CAM designs. By confining the high‑energy pre‑charge operation to a subset of lines that have already passed a coarse three‑bit filter, the architecture dramatically reduces the average dynamic power without sacrificing search latency.

The authors fabricated a 256 × 144‑bit array in TSMC 90 nm CMOS. Post‑layout Monte‑Carlo simulations, including process, voltage, and temperature (PVT) corners, demonstrate robust operation across a supply range of 0.9 V to 1.1 V and a temperature span of –40 °C to 125 °C. The measured energy per search is 0.115 fJ per bit, which is among the lowest reported for CAMs of comparable size and speed. The search time is 361.6 ps, allowing a maximum operating frequency of 1 GHz. Compared with conventional fully‑energized CAMs and recent power‑gating schemes, SMLE‑CAM achieves a 30 %–40 % reduction in dynamic power while maintaining equal or slightly better latency.

The paper also discusses limitations. Because the power‑saving mechanism relies on the first three bits, data sets with biased or non‑uniform distributions in those positions may see reduced energy benefits. Moreover, the SMLE circuitry adds roughly 12 % area overhead relative to a baseline CAM, a trade‑off that may be critical in area‑constrained applications. The authors propose future extensions such as variable‑length pre‑filter blocks, multi‑stage selective energizers, and integration with higher‑level memory controllers to further improve adaptability and scalability.

In summary, SMLE‑CAM presents a compelling approach to CAM power reduction by introducing selective line energization based on early‑stage XNOR/XOR comparison. The architecture delivers state‑of‑the‑art energy efficiency (0.115 fJ/bit/search) and sub‑nanosecond search speed, validated through extensive post‑layout simulations and PVT robustness analysis. The work opens a promising pathway for energy‑aware CAM designs in networking, database acceleration, and emerging neuromorphic systems.