High Throughput and Less Area AMP Architecture for Audio Signal Restoration

Audio restoration is effectively achieved by using low complexity algorithm called AMP. This algorithm has fast convergence and has lower computation intensity making it suitable for audio recovery problems. This paper focuses on restoring an audio signal by using VLSI architecture called AMP-M that implements AMP algorithm. This architecture employs MAC unit with fixed bit Wallace tree multiplier, FFT-MUX and various memory units (RAM) for audio restoration. VLSI and FPGA implementation results shows that reduced area, high throughput, low power is achieved making it suitable for real time audio recovery problems. Prominent examples are Magnetic Resonance Imaging (MRI), Radar and Wireless Communications.

💡 Research Summary

The paper presents a VLSI implementation of the Approximate Message Passing (AMP) algorithm tailored for real‑time audio signal restoration, termed AMP‑M. Starting from the compressed‑sensing model z = Ax + Be, the authors argue that many audio degradations (narrow‑band interference, clicks, pops) can be represented as sparse vectors, making AMP an attractive low‑complexity recovery method. After reviewing a broad set of sparse recovery algorithms, they select AMP for its fast convergence and lack of prior information requirements.

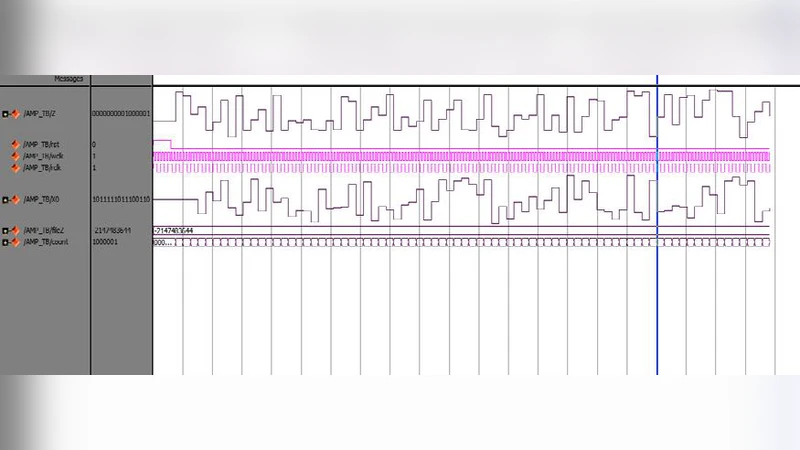

The proposed architecture consists of several dedicated blocks: a 16‑bit fixed‑point Wallace‑tree multiplier‑based MAC unit for the matrix‑vector products, an FFT‑MUX module that performs DCT/IDCT‑based M/2 length FFT/IFFT on the residuals, multiple RAMs (Z‑RAM, X‑RAM, FFT‑RAM) for storing intermediate vectors, a thresholding unit (TR‑SH‑L0) implementing the non‑linear η function, and an RMS‑error unit that drives an Early Termination (ET) controller. The ET logic stops the iterative process as soon as the RMS error falls below a preset threshold, typically after no more than 28 iterations.

Simulation using 512‑point DCT blocks on 44.1 kHz 16‑bit stereo audio demonstrates that the hardware achieves comparable or better restoration quality than software baselines while maintaining a very low iteration count. The design is synthesized on an Altera Cyclone III DE0 board (15 408 logic elements), consuming only 3 693 elements (≈24 % of the device), 65.43 mW of power, and operating at 408.5 MHz. A comparison with an equivalent implementation in 65 nm CMOS IP8M technology shows a three‑fold power reduction and a 22 % increase in throughput.

The authors conclude that AMP‑M offers a compact, low‑power, high‑throughput solution for compressed‑sensing‑based signal restoration, suitable not only for audio but also for MRI, radar, and wireless communication applications. Future work includes extending the design to higher‑precision audio (24‑bit/96 kHz), supporting arbitrary measurement matrices, and migrating the architecture to an ASIC for further area and power savings.

Comments & Academic Discussion

Loading comments...

Leave a Comment