Generating and evaluating application-specific hardware extensions

Modern platform-based design involves the application-specific extension of embedded processors to fit customer requirements. To accomplish this task, the possibilities offered by recent custom/extensible processors for tuning their instruction set and microarchitecture to the applications of interest have to be exploited. A significant factor often determining the success of this process is the utomation available in application analysis and custom instruction generation. In this paper we present YARDstick, a design automation tool for custom processor development flows that focuses on generating and evaluating application-specific hardware extensions. YARDstick is a building block for ASIP development, integrating application analysis, custom instruction generation and selection with user-defined compiler intermediate representations. In a YARDstick-enabled environment, practical issues in traditional ASIP design are confronted efficiently; the exploration infrastructure is liberated from compiler and simulator idiosyncrasies, since the ASIP designer is empowered with the freedom of specifying the target architectures of choice and adding new implementations of analyses and custom instruction generation/selection methods. To illustrate the capabilities of the YARDstick approach, we present interesting exploration scenarios: quantifying the effect of machine-dependent compiler optimizations and the selection of the target architecture in terms of operation set and memory model on custom instruction generation/selection under different input/output constraints.

💡 Research Summary

The paper presents YARDstick, an automation framework designed to streamline the generation and evaluation of application‑specific hardware extensions for ASIP (Application‑Specific Instruction‑set Processor) development. Modern platform‑based design increasingly relies on extending embedded processors to meet particular customer requirements, but the success of such extensions hinges on the availability of tools that can analyze applications and automatically synthesize custom instructions (CIs). Existing flows are often tightly coupled to specific compilers or simulators, limiting flexibility and making design‑space exploration cumbersome.

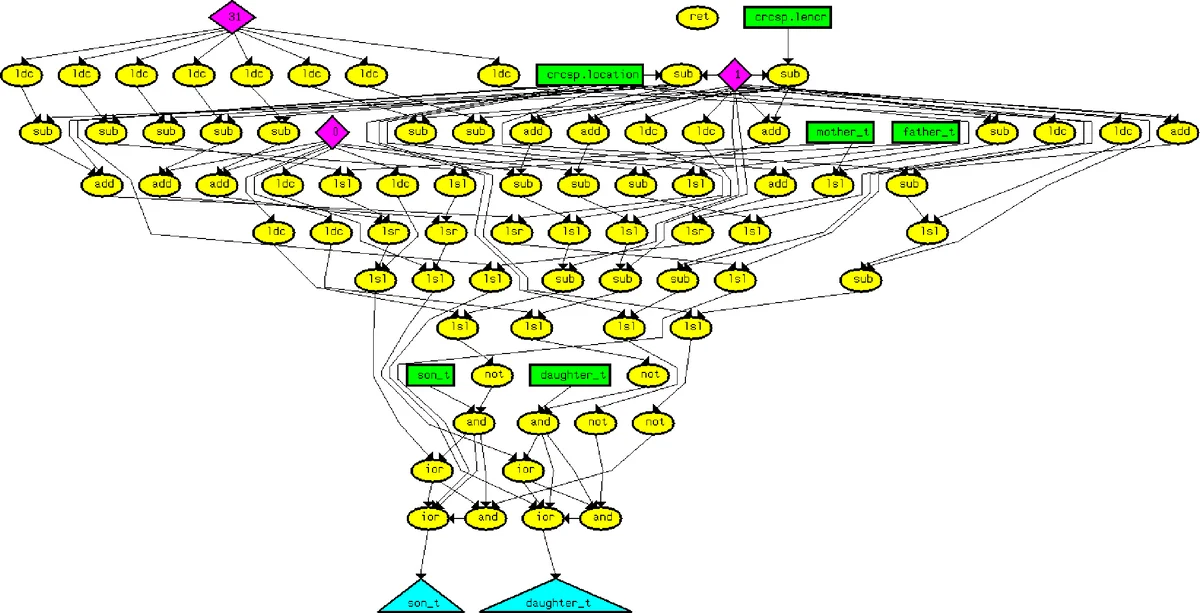

YARDstick addresses these challenges by providing a modular kernel composed of three libraries—libByoX, libPatCUTE, and libmachine—together with a target‑architecture description format called BXIR. libByoX implements the core API, parsing flat CDFG (ISeq) and control‑flow graph (CFG) files, exposing operand‑level information, register lifetimes, loop structures, and other static/dynamic metrics. Crucially, it allows designers to plug in arbitrary intermediate representations (IRs), removing the dependence on any particular compiler’s IR. libPatCUTE houses pattern‑based CI generation and selection algorithms. It supports MAXMISO (maximal single‑output subgraph) discovery with linear complexity, constrained MISO exploration (limited numbers of inputs/outputs), and a heuristic MIMO (multiple‑input‑multiple‑output) search that assumes any sub‑pattern yields less performance gain than its superset. Users may optionally switch to an exhaustive exponential search. After pattern extraction, CI candidates are filtered for redundancy via graph‑isomorphism tests and then ranked using configurable metrics such as cycle‑gain, area‑efficiency, or a 0‑1 knapsack formulation. libmachine is the only component that must be retargeted for a new ISA; it reads BXIR files that describe the operation set, data‑type semantics, and per‑operation cost models (area, latency, cycle count).

The framework supplies a suite of back‑ends that export generated artifacts to various formats: ANSI‑C subsets for integration into simulators, Graphviz DOT or VCG files for visualization, an extended CDFG format for scheduling and VHDL synthesis, and GGX XML for algebraic graph transformations. This enables seamless flow from high‑level application code (C/C++) through a conventional compiler front‑end (e.g., GCC), optional assembly‑level instrumentation, conversion to ISeq via a SALTO pass, and finally into YARDstick for profiling and CI generation. Dynamic profiling data (basic‑block execution frequencies, cache accesses, etc.) can be fed back to refine CI selection.

The authors validate YARDstick through three case studies involving different IR configurations: an enhanced SUIFvm with bit‑manipulation extensions (SUIFvmenh), a finite‑register variant of SUIF (SUIF rmenh), and a simple integer DLX subset (iDLX). Benchmarks include CRC, IDEA, SHA‑1, ADPCM encoder/decoder, FIR filter, and motion‑estimation kernels. Experiments reveal that richer IRs containing bit‑level operations dramatically increase the number of viable MIMO patterns, leading to higher speed‑ups, while a limited register file favors MAXMISO patterns due to reduced operand availability. Moreover, altering the memory model (e.g., varying load/store costs) or imposing different input/output operand constraints reshapes the optimal CI set, underscoring the importance of exploring these parameters during ASIP design.

Compared with prior work such as Pattlib, Xtensa‑based CI generators, and multi‑output instruction selection frameworks, YARDstick distinguishes itself by decoupling the exploration infrastructure from any specific compiler or simulator, supporting arbitrary IRs, and offering a plug‑in architecture for custom analyses and cost models. Limitations noted include the manual effort required to author BXIR descriptions and integrate third‑party synthesis tools, as well as the need for further scalability studies on large‑scale applications.

In conclusion, YARDstick provides a flexible, extensible platform that empowers ASIP designers to perform rapid, architecture‑agnostic design‑space exploration, quantify the impact of compiler optimizations, and systematically evaluate custom hardware extensions under diverse architectural and memory‑model constraints. Future work is suggested in automating BXIR cost generation, incorporating machine‑learning‑driven pattern discovery, and extending the framework to support heterogeneous multi‑core and accelerator‑rich systems.

Comments & Academic Discussion

Loading comments...

Leave a Comment