Instruction-set Selection for Multi-application based ASIP Design: An Instruction-level Study

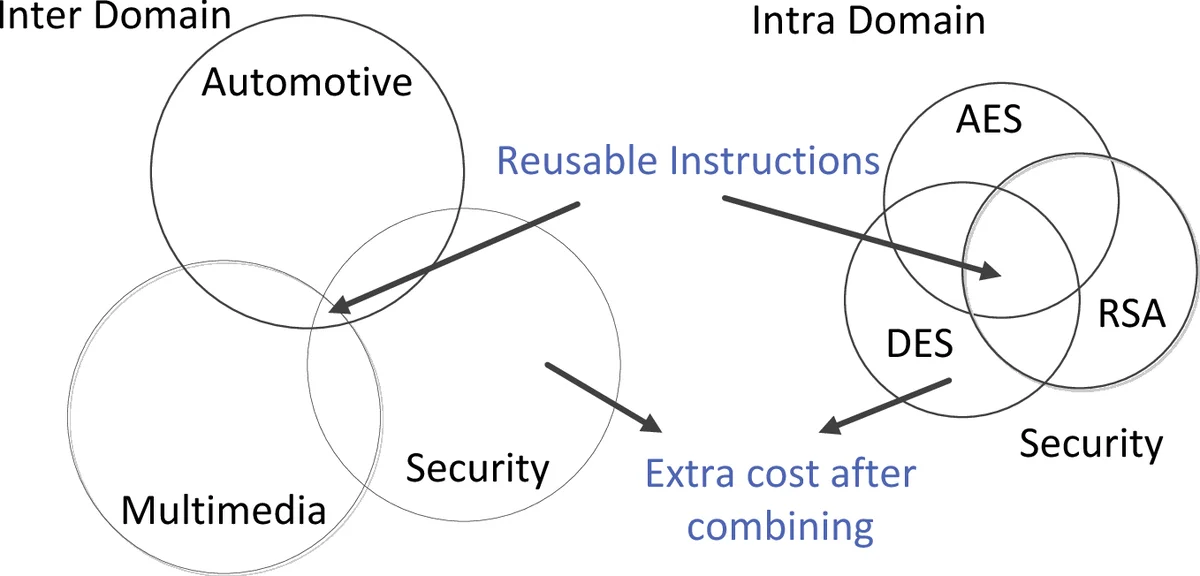

Efficiency in embedded systems is paramount to achieve high performance while consuming less area and power. Processors in embedded systems have to be designed carefully to achieve such design constraints. Application Specific Instruction set Processors (ASIPs) exploit the nature of applications to design an optimal instruction set. Despite being not general to execute any application, ASIPs are highly preferred in the embedded systems industry where the devices are produced to satisfy a certain type of application domain/s (either intra-domain or inter-domain). Typically, ASIPs are designed from a base-processor and functionalities are added for applications. This paper studies the multi-application ASIPs and their instruction sets, extensively analysing the instructions for inter-domain and intra-domain designs. Metrics analysed are the reusable instructions and the extra cost to add a certain application. A wide range of applications from various application benchmarks (MiBench, MediaBench and SPEC2006) and domains are analysed for two different architectures (ARM-Thumb and PISA). Our study shows that the intra-domain applications contain larger number of common instructions, whereas the inter-domain applications have very less common instructions, regardless of the architecture (and therefore the ISA).

💡 Research Summary

The paper investigates how to select instruction sets for multi‑application specific instruction‑set processors (ASIPs), focusing on the trade‑off between instruction reuse and the extra cost of adding new instructions when supporting multiple applications. The authors argue that while ASIPs are already a compromise between the efficiency of ASICs and the flexibility of FPGAs, designing an ASIP that can handle several applications—especially from different domains—requires a careful analysis of which instructions are common across the target workloads and which must be added as extensions.

To this end, the authors conduct an extensive empirical study using two well‑known instruction set architectures (ISAs): ARM‑Thumb (78 integer‑type instructions) and PISA (72 integer‑type instructions). They select a broad set of benchmark applications from three widely used suites—MiBench, MediaBench, and SPEC2006—covering six domains: Automotive, Office, Security, Telecom, MediaBench, and SPEC CPU integer workloads. For each domain, four representative applications are chosen, resulting in a total of 24 applications.

The experimental methodology consists of compiling each application with the appropriate cross‑compiler for the target ISA, extracting the generated assembly, and counting the distinct instructions used. For each domain, three numbers are computed: (i) the number of instructions used by each individual application, (ii) the size of the intersection (i.e., the set of instructions common to all four applications in that domain), and (iii) the size of the union (i.e., the total distinct instructions required to support all four applications). Two quantitative metrics are defined:

-

Reusability Factor = (Number of instructions in the base ISA) / (Total number of instructions in the mASIP) × 100.

This measures how much of the instruction set can be shared across the target applications. -

Extra‑Cost Factor =

Comments & Academic Discussion

Loading comments...

Leave a Comment