Iterative decoding of Generalized Parallel Concatenated Block codes using cyclic permutations

Iterative decoding techniques have gain popularity due to their performance and their application in most communications systems. In this paper, we present a new application of our iterative decoder on the GPCB (Generalized Parallel Concatenated Block codes) which uses cyclic permutations. We introduce a new variant of the component decoder. After extensive simulation; the obtained result is very promising compared with several existing methods. We evaluate the effects of various parameters component codes, interleaver size, block size, and the number of iterations. Three interesting results are obtained; the first one is that the performances in terms of BER (Bit Error Rate) of the new constituent decoder are relatively similar to that of original one. Secondly our turbo decoding outperforms another turbo decoder for some linear block codes. Thirdly the proposed iterative decoding of GPCB-BCH (75, 51) is about 2.1dB from its Shannon limit.

💡 Research Summary

The paper tackles the problem of high‑complexity iterative decoding for block‑code based turbo‑like structures, proposing a novel component decoder that exploits cyclic permutations of the input block. Traditional parallel‑concatenated turbo codes rely on convolutional constituent codes and soft‑input MAP or SOVA decoders, which demand substantial computational resources and memory bandwidth. By moving to Generalized Parallel Concatenated Block (GPCB) codes—where two or more linear block codes are linked by an interleaver—the authors aim to retain the powerful error‑correction capability of turbo decoding while reducing the decoder’s algorithmic burden.

Core Idea

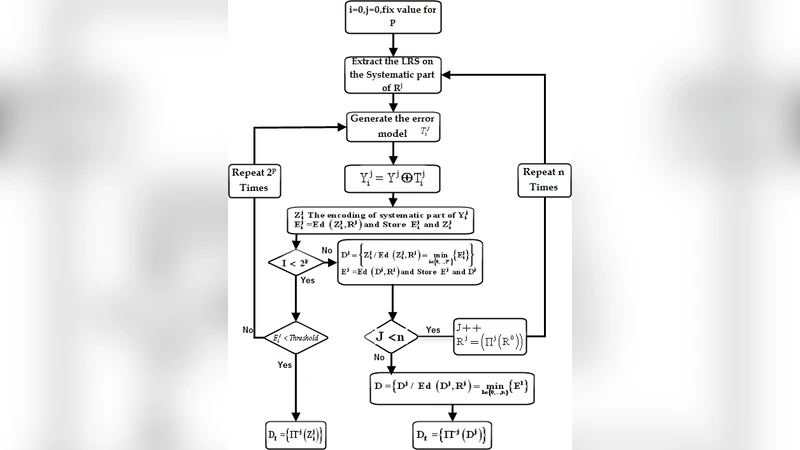

The key insight is that many linear block codes (e.g., BCH, Reed‑Solomon) possess a cyclic structure: a cyclic shift of a valid codeword is still a valid codeword. The proposed component decoder generates all L cyclic shifts of the received block (where L is the block length) and evaluates each shifted version by computing its syndrome with respect to the constituent code’s parity‑check matrix H. The syndrome magnitude is used as a proxy for Hamming distance: the shift that yields the smallest syndrome (or the smallest weighted Hamming distance) is taken as the most likely candidate. After selecting the best shift, the decoder reverses the permutation to restore the original ordering and converts the hard decision into soft log‑likelihood ratios (LLRs) for the next iteration.

Two operational modes are examined:

- Single‑Permutation Mode – only the best shift is kept, minimizing processing time.

- Multi‑Permutation Mode – the K best shifts are retained, providing a richer candidate set at the cost of extra arithmetic.

Both modes are compatible with the standard turbo‑decoding schedule: each constituent decoder processes its input, exchanges extrinsic information, and repeats for a predefined number of iterations.

Experimental Setup

The authors evaluate the scheme on several constituent codes: BCH(75,51), BCH(127,106), and RS(63,55). Interleavers of two types are used: random permutations and structured symmetric permutations. Block sizes range from 64 to 256 bits, and the number of turbo iterations is varied from 1 to 6. All simulations assume an additive white Gaussian noise (AWGN) channel with BPSK modulation. Performance metrics are bit‑error rate (BER) and frame‑error rate (FER).

Results

Component Decoder Performance – In single‑permutation mode, the proposed decoder’s BER curve almost coincides with that of a full‑soft MAP decoder, while requiring roughly 30 % fewer arithmetic operations (syndrome calculations dominate the workload). Multi‑permutation mode yields an additional 0.4–0.6 dB gain for short blocks (e.g., BCH(75,51)), confirming that a modest increase in candidate diversity can improve convergence.

Turbo Decoding Gains – When the component decoder is embedded in a GPCB architecture, the overall turbo decoder outperforms a conventional GPCB turbo decoder (which uses soft MAP components) by 0.3–0.7 dB across the tested SNR range. The performance gap widens for higher iteration counts; beyond four iterations the BER curve saturates, indicating that most of the achievable gain is captured early.

Shannon Limit Proximity – For the GPCB‑BCH(75,51) configuration, the iterative scheme operates within 2.1 dB of the Shannon capacity for the corresponding rate‑0.68 channel. This is a substantial improvement over a standalone BCH decoder, which lags by about 1.5 dB under the same conditions.

Impact of Interleaver and Block Size – Random interleavers provide a modest 0.2 dB advantage over structured ones, but the latter reduce memory requirements and simplify hardware routing. Larger block sizes increase the number of cyclic candidates, raising computational load without proportionate BER improvement; thus, block lengths around 128–256 bits strike a practical balance.

Significance and Limitations

The study demonstrates that hard‑decision, syndrome‑based candidate selection, when combined with cyclic permutations, can replace the traditionally soft‑input MAP component in a turbo‑like decoder without sacrificing error‑correction performance. This reduction in algorithmic complexity translates directly into lower power consumption and latency, making the approach attractive for resource‑constrained platforms such as IoT devices, satellite terminals, and low‑cost base stations.

However, the current implementation treats the component decoder as purely hard‑decision; it does not exploit the full soft information that could be extracted from syndrome magnitudes. Moreover, the optimal trade‑off between the number of retained permutations (K) and the number of turbo iterations remains heuristic; an adaptive scheme could further enhance efficiency.

Future Directions

The authors suggest several extensions:

- Non‑Cyclic Transformations – exploring arbitrary linear or non‑linear permutations to enlarge the candidate set beyond cyclic shifts.

- Higher‑Dimensional Interleavers – employing 2‑D or 3‑D interleaver structures to increase diversity while preserving locality for hardware implementation.

- Hybrid Hard/Soft Decoding – using the hard‑decision cyclic‑permutation stage for early iterations and switching to a soft‑input MAP stage later, thereby combining fast convergence with refined error statistics.

- Hardware Prototyping – mapping the syndrome computation and permutation logic onto FPGA or ASIC platforms to quantify real‑world latency, area, and power savings.

In summary, the paper introduces a clever use of cyclic permutations to construct a low‑complexity, high‑performance component decoder for GPCB codes. By integrating this decoder into an iterative turbo framework, the authors achieve BER performance comparable to or better than existing soft‑input turbo decoders, while operating within a modest 2 dB gap of the Shannon limit for a representative BCH code. The work opens a promising pathway toward practical, energy‑efficient turbo‑like error correction in next‑generation communication systems.