Boolean Satisfiability using Noise Based Logic

In this paper, we present a novel algorithm to solve the Boolean Satisfiability (SAT) problem, using noise-based logic (NBL). Contrary to what the name may suggest, NBL is not a random/fuzzy logic system. In fact, it is a completely deterministic logic system. A key property of NBL is that it allows us to apply a superposition of many input vectors to a SAT instance at the same time, circumventing a key restriction and assumption in the traditional approach to solving SAT. By exploiting the superposition property of NBL, our NBL-based SAT algorithm can determine whether an instance is SAT or not in a single operation. A satisfying solution can be found by iteratively performing SAT check operations up to n times, where n is the number of variables in the SAT instance. Although this paper does not focus on the realization of an NBL-based SAT engine, such an engine can be conceived using analog circuits (wide-band amplifiers, adders and multipliers), FPGAs or ASICs. Additionally, we also discus scalability of our approach, which can apply to NBL in general. The NBL-based SAT engine described in this paper has been simulated in software for validation purposes.

💡 Research Summary

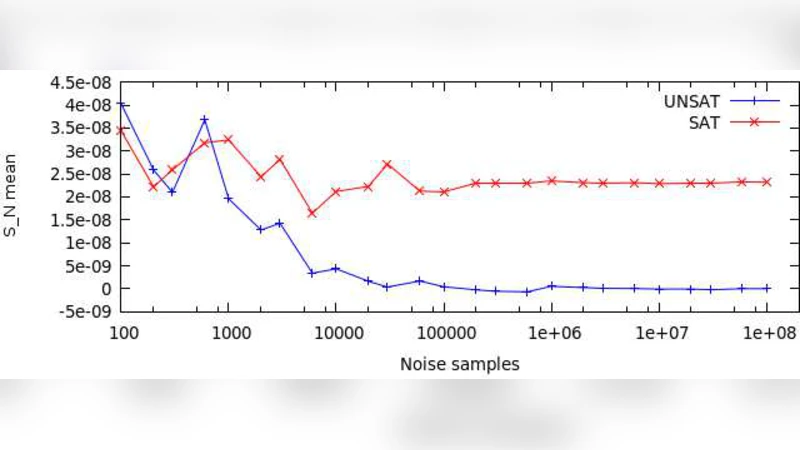

The paper introduces a deterministic “noise‑based logic” (NBL) framework for solving Boolean satisfiability (SAT). NBL employs a set of pairwise orthogonal noise sources—called noise bits—whose products generate a hyperspace of size 2ⁿ. By adding any subset of these hyperspace elements on a single wire, the system can represent the superposition of all 2ⁿ possible input assignments simultaneously. The authors map a CNF SAT instance S to an NBL formula S_N consisting of two parts: τ_N, which encodes all 2ⁿ minterms using products of noise bits across all clauses, and Σ_N, which encodes the original clauses by replacing each literal with a “cube subspace” built from the appropriate noise‑bit products. When Σ_N is expanded, only those minterms that satisfy every clause survive as non‑zero signals; thus, a single measurement of the average signal of Σ_N determines SAT/UNSAT in O(1) time. To extract a concrete satisfying assignment, the algorithm fixes one variable at a time (to 0 or 1), rebuilds the superposition for the remaining variables, and repeats the SAT‑check. In the worst case this requires n iterations, yielding a linear‑time solution‑recovery procedure. The paper discusses practical realizations using wide‑band analog amplifiers, adders, multipliers, and low‑pass filters, as well as possible FPGA/ASIC implementations. MATLAB simulations on small CNF examples confirm that the method correctly distinguishes satisfiable from unsatisfiable instances and recovers a satisfying assignment. Compared with quantum‑computing approaches, NBL offers a similar superposition capability but relies on existing analog/digital hardware rather than fragile quantum devices. The authors acknowledge challenges such as maintaining perfect orthogonality of noise bits, signal‑to‑noise ratio management, and scaling circuit complexity with the number of variables and clauses. Overall, the work proposes a novel, theoretically sound paradigm that reduces SAT decision to a single NBL operation and solution extraction to a linear number of operations, opening a new direction for hardware‑accelerated SAT solving.

Comments & Academic Discussion

Loading comments...

Leave a Comment