Time-domain approach to energy efficiency in high-performance network element design

Energy efficiency is a corner stone of sustainability in data center and high-performance networking. However, at present there is a notable structural mismatch between network silicon development targets and network equipment utilization patterns in the field. In particular, some aspects of network energy utilization (eg load-proportional energy consumption) routinely stay out of focus during system design and implementation. Drawing from hands-on research and development in high-speed and grid networking, we identify a novel approach to energy efficiency in network engineering. In this paper, we demonstrate how the problem of efficient network system design can be dissected into smaller sections based on timescales of traffic processing. The newly proposed approach allows R&D efforts to be tightly paired to resources and sustainability targets to improve energy efficiency in many classes of network and telecom devices.

💡 Research Summary

The paper addresses the growing mismatch between the design focus of high‑performance networking hardware and the actual utilization patterns observed in data‑center and carrier environments. While silicon development has historically emphasized peak‑load efficiency—measured in watts per gigabit—the authors point out that real‑world traffic typically operates at 30‑50 % of nominal capacity, leaving a large proportion of energy consumption untapped. To bridge this gap, the authors propose a “time‑domain” methodology that decomposes the energy‑efficiency problem into three distinct temporal scales, each requiring a tailored design and management strategy.

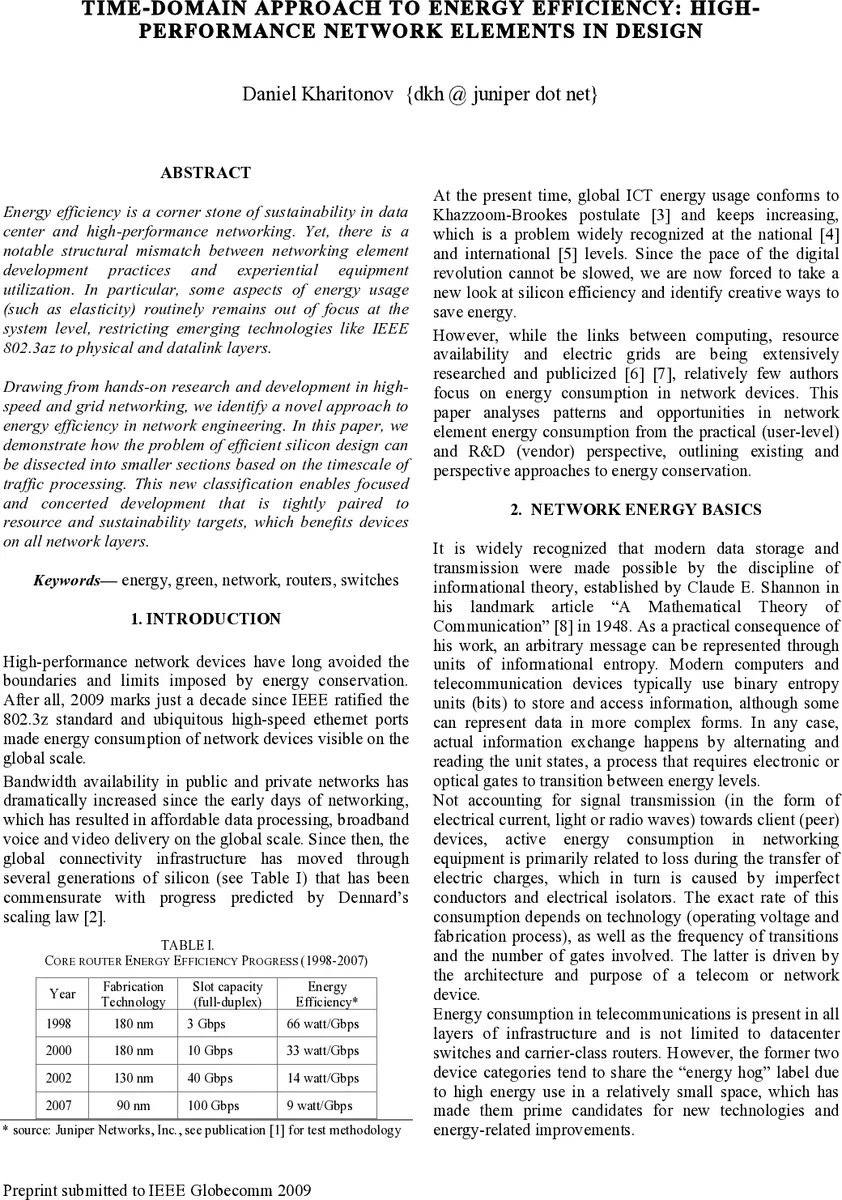

Peak‑Energy Domain – This domain concerns the hardware’s behavior when fully loaded. Using measurements from Juniper’s T1600 core router and MX960 Ethernet router, the paper shows that power consumption rises only modestly (≈7 % increase) from idle to full load, indicating that peak efficiency is already high. However, the baseline power draw at low load remains non‑trivial, and thermal limits still constrain further scaling of speed and density.

Low‑Load / Delay‑Variable Energy Domain – Here the focus shifts to link‑level power management, leveraging the IEEE 802.3az Energy‑Efficient Ethernet standard. By negotiating low‑power idle (LPI) states and keeping transition latencies (Ts for sleep, Tw for wake) below 30 µs, a link can cut its power consumption by up to 80 % during idle periods without violating service‑level agreements. The authors extrapolate that extending this mechanism to the entire line‑card could yield a 20‑30 % reduction in overall system power for a modest 10 % budget increase dedicated to link‑state control logic.

Packet‑Loss / Delay‑Variable Energy Domain – The third domain examines intra‑card components such as ASIC forwarding planes, CPUs, and memory banks. By dynamically gating power to these blocks based on permissible jitter (e.g., 10 ms for video, 30 ms for voice) and the maximum tolerable application‑level delay (Tsla), substantial portions of the silicon can be placed in low‑power or off states during periods of reduced traffic. The paper quantifies potential savings of 15‑35 % in total power, noting that the trade‑off is governed by the relationship Tsla ≤ Ts + Tw.

A key insight throughout the work is the self‑similar, bursty nature of network traffic, which forces any design to retain full peak capacity at all times while still offering opportunities for energy proportionality during the long stretches of under‑utilization. The authors therefore advocate a multi‑layered power‑management framework: (1) maintain a robust, high‑speed data path for peak bursts; (2) employ link‑level LPI states to capture the bulk of idle energy; (3) apply fine‑grained, delay‑aware gating inside the line card to shave off the remaining “energy hog” consumption.

The paper concludes with a roadmap for future work: accelerating the commercialization of 802.3az‑compatible PHYs, developing microsecond‑scale power‑gate circuits for ASICs, and integrating the proposed methodology into broader data‑center and carrier‑network energy‑efficiency standards. By adopting this time‑domain approach, next‑generation 400 Gbps and 800 Gbps routers and switches could achieve meaningful operational‑cost reductions and carbon‑footprint improvements, aligning high‑performance networking with sustainability goals.

Comments & Academic Discussion

Loading comments...

Leave a Comment