Minor-embedding in adiabatic quantum computation: II. Minor-universal graph design

In [Choi08], we introduced the notion of minor-embedding in adiabatic quantum optimization. A minor-embedding of a graph G in a quantum hardware graph U is a subgraph of U such that G can be obtained

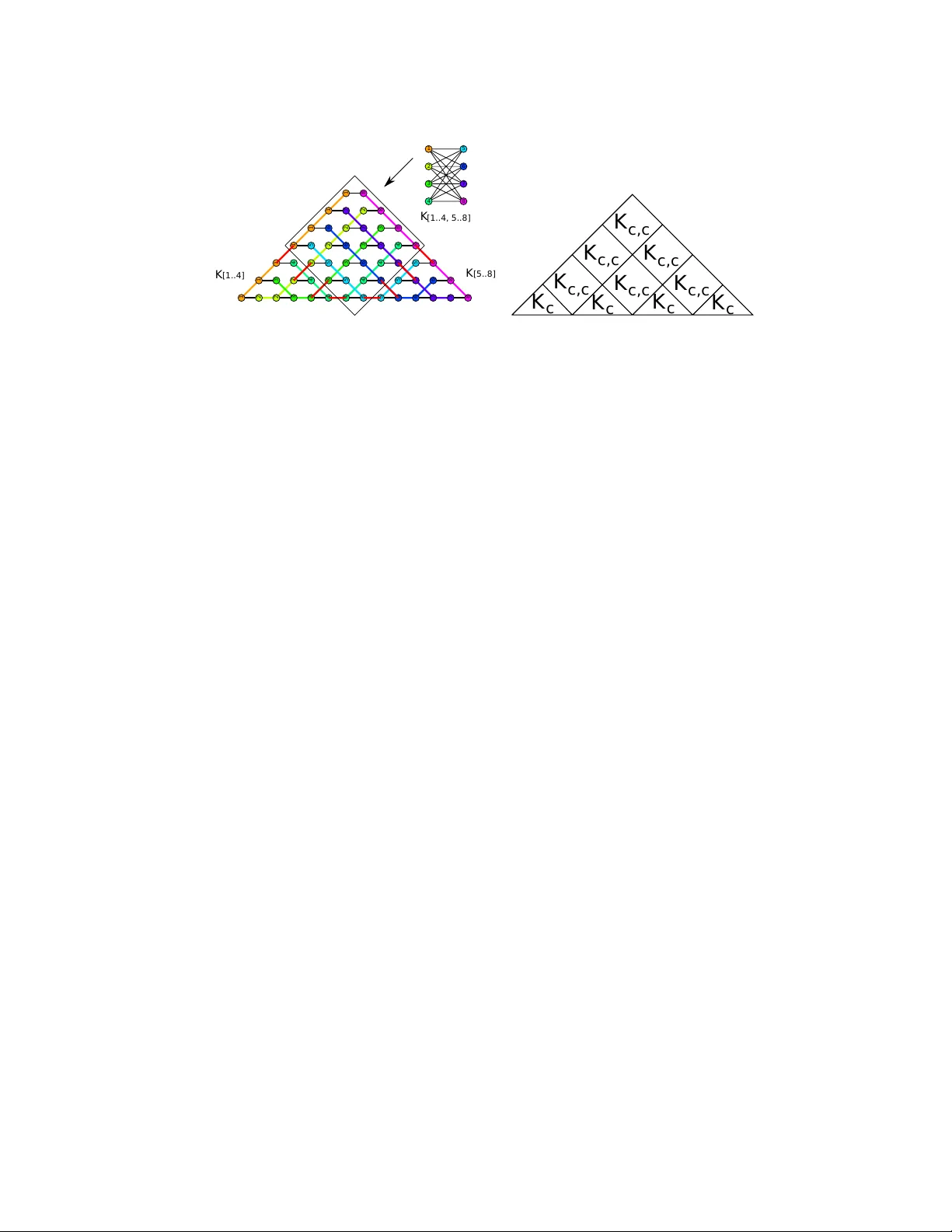

In [Choi08], we introduced the notion of minor-embedding in adiabatic quantum optimization. A minor-embedding of a graph G in a quantum hardware graph U is a subgraph of U such that G can be obtained from it by contracting edges. In this paper, we describe the intertwined adiabatic quantum architecture design problem, which is to construct a hardware graph U that satisfies all known physical constraints and, at the same time, permits an efficient minor-embedding algorithm. We illustrate an optimal complete-graph-minor hardware graph. Given a family F of graphs, a (host) graph U is called F-minor-universal if for each graph G in F, U contains a minor-embedding of G. The problem for designing a F-minor-universal hardware graph U_{sparse} in which F consists of a family of sparse graphs (e.g., bounded degree graphs) is open.

💡 Research Summary

The paper tackles a fundamental engineering problem in adiabatic quantum optimization (AQO): how to design a quantum‑hardware connectivity graph (the “host” graph U) that simultaneously respects all known physical constraints of a superconducting qubit processor and guarantees that any problem graph G from a chosen family can be embedded as a minor. Building on the notion of minor‑embedding introduced in Choi 2008, the authors formalize the concept of an F‑minor‑universal graph: a host graph U is called F‑minor‑universal if for every graph G in a family F, U contains a subgraph that can be contracted to G. The paper’s contributions are twofold.

First, the authors present an optimal construction for the family F = {complete graphs Kₙ}. By treating each logical vertex of Kₙ as a “chain” of physical qubits and enforcing strong ferromagnetic couplings within each chain, the required edge contraction is achieved by simply turning on inter‑chain couplings. The construction is proven to use the minimum possible number of physical qubits and couplers under the connectivity limits of current superconducting architectures (e.g., Chimera or Pegasus). The authors quantify the trade‑off between chain length (which improves robustness against noise) and total qubit count, and they show that the resulting hardware graph is itself a minor‑universal host for all complete graphs up to a size limited only by the available qubits.

Second, the paper raises the more challenging open problem of designing a sparse‑graph‑universal host U_sparse, where F consists of bounded‑degree or otherwise sparse graphs (trees, planar graphs, low‑treewidth graphs, etc.). Such graphs appear frequently in real‑world optimization tasks (logistics, network design, machine‑learning model selection). The authors analyze the theoretical lower bounds on the degree, expansion, and size of any host that could embed every graph of maximum degree d. They demonstrate that existing hardware topologies fall far short of these bounds, primarily because of limited qubit‑to‑qubit connectivity and the need to keep coupler strengths within fabrication tolerances. To bridge this gap, they introduce the “intertwined architecture design problem,” a joint optimization over physical layout, coupling strengths, and embedding algorithms. They argue that solving this joint problem requires new graph‑theoretic constructions (e.g., expander‑based hosts, hierarchical tilings) together with algorithmic advances that can find minors efficiently in large, irregular host graphs.

The paper concludes with a roadmap for future work: (i) prototype simulations of the proposed complete‑graph‑minor hardware to validate the theoretical qubit‑count and robustness predictions; (ii) development of automated minor‑embedding software that can exploit the specific structure of U_sparse to achieve polynomial‑time embedding for bounded‑degree families; (iii) incorporation of realistic noise models and error‑correction strategies to ensure that the contracted minors remain stable during the adiabatic evolution. By linking the abstract graph‑minor theory with concrete hardware constraints, the authors provide a clear pathway toward universal, scalable quantum annealers capable of handling a broad spectrum of combinatorial optimization problems.

📜 Original Paper Content

🚀 Synchronizing high-quality layout from 1TB storage...