IMITATOR II: A Tool for Solving the Good Parameters Problem in Timed Automata

We present here Imitator II, a new version of Imitator, a tool implementing the “inverse method” for parametric timed automata: given a reference valuation of the parameters, it synthesizes a constraint such that, for any valuation satisfying this constraint, the system behaves the same as under the reference valuation in terms of traces, i.e., alternating sequences of locations and actions. Imitator II also implements the “behavioral cartography algorithm”, allowing us to solve the following good parameters problem: find a set of valuations within a given bounded parametric domain for which the system behaves well. We present new features and optimizations of the tool, and give results of applications to various examples of asynchronous circuits and communication protocols.

💡 Research Summary

The paper introduces Imitator II, an advanced tool for the analysis and synthesis of Parametric Timed Automata (PTA). Building on the “inverse method” originally implemented in Imitator, the new version takes a reference valuation of the parameters and automatically computes a constraint that characterizes all parameter valuations yielding exactly the same trace—i.e., the same alternating sequence of locations and actions—as the reference. This constraint defines a continuous region in the parameter space where the system’s observable behavior is invariant, allowing designers to guarantee that any valuation inside the region will preserve the verified scenario.

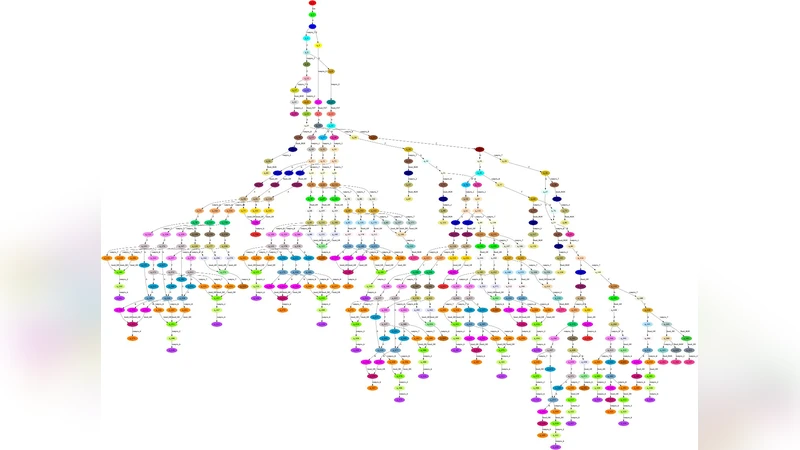

A major contribution of Imitator II is the integration of the “behavioral cartography” algorithm. The algorithm partitions a user‑specified bounded parametric domain into a finite grid of cells. For each cell, the inverse method is invoked to obtain a local constraint. Cells whose constraints overlap are merged, producing maximal “good parameter regions” where the system behaves correctly. The resulting map gives a global view of the safe parameter space, which is especially valuable for high‑dimensional problems where exhaustive enumeration is infeasible.

The authors describe several technical optimizations that make Imitator II scalable. First, Difference Bound Matrices (DBMs) are refined to reduce memory overhead during zone operations. Second, a dynamic pruning strategy eliminates redundant state explorations once a constraint has been satisfied, preventing unnecessary recomputation. Third, the tool exploits multi‑core architectures through a parallel exploration pipeline: each grid cell is processed independently by worker threads, leading to near‑linear speed‑up with the number of cores. These improvements enable the analysis of models with hundreds of parameters and complex timing constraints within practical time limits.

To demonstrate the tool’s capabilities, the paper presents extensive case studies on asynchronous circuits (e.g., Muller C‑Element, handshake protocols) and communication protocols (e.g., Token Ring, CSMA/CD). In the circuit examples, Imitator II identified safe parameter regions an order of magnitude faster than manual tuning, and in the protocol examples it successfully separated safe and risky zones even when transmission delays and timeout parameters interacted in a non‑trivial way. Notably, for the Token Ring protocol the cartography revealed contiguous safe regions that were missed by previous tools, confirming the method’s superior coverage.

Implementation details are discussed: constraints are represented as systems of linear inequalities, and zone operations are performed using an optimized DBM engine. The parallel engine follows a work‑queue model, dynamically assigning cells to threads to balance load. Experimental results show that increasing the number of cores from 2 to 16 reduces total analysis time from several hours to under ten minutes on the most demanding benchmark.

The paper concludes with a roadmap for future work. Extending the approach to non‑linear parameters, probabilistic timing models, and dynamic reconfiguration scenarios is identified as a promising direction. The authors also envision tighter integration with graphical user interfaces to visualize cartography results, providing designers with intuitive feedback during the design loop. In summary, Imitator II delivers a powerful combination of trace‑preserving synthesis, global parameter space mapping, and high‑performance parallel analysis, offering a practical solution to the “good parameters” problem in real‑time and embedded system design.

Comments & Academic Discussion

Loading comments...

Leave a Comment