Fourier Domain Analysis performances of a RESPER probe - Amplitude and Phase inaccuracies due to the Round-Off noise of FFT processors

This report proposes to discuss the Fourier domain analysis performances of a RESPER probe. A uniform ADC, which is characterized by a sensible phase inaccuracy depending on frequency, is connected to a Fast Fourier Transform (FFT) processor, that is especially affected by a round-off amplitude noise linked to both the FFT register length and samples number. If the register length is equal to 32 bits, then the round-off noise is entirely negligible, else, once bits are reduced to 16, a technique of compensation must occur. In fact, oversampling can be employed within a short time window, reaching a compromise between the needs of limiting the phase inaccuracy due to ADC and not raising too much the number of averaged FFT values sufficient to bound the round-off. Finally, the appendix presents an outline of somewhat lengthy demonstrations needed to calculate the amplitude and especially phase inaccuracies due to the round-off noise of FFT processors.

💡 Research Summary

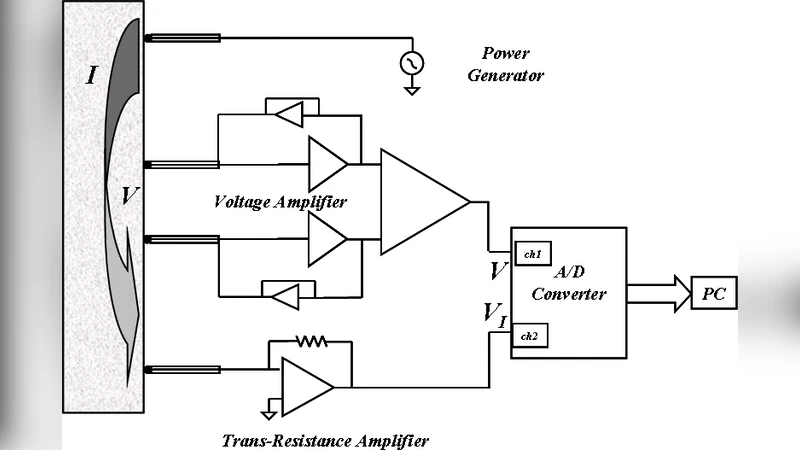

The paper investigates the combined impact of a uniform 12‑bit analog‑to‑digital converter (ADC) and a Fast Fourier Transform (FFT) processor on the measurement accuracy of a RESPER (Resistivity‑Permittivity) probe. The authors begin by characterizing the ADC’s phase error, which grows with frequency due to quantization noise inherent in uniform sampling. This phase inaccuracy is particularly problematic for low‑frequency complex impedance measurements where precise phase information is essential.

Attention then shifts to the FFT stage, where the dominant source of error is round‑off noise generated by finite‑length arithmetic registers. Two key parameters govern this noise: the register bit‑width (B) and the number of time‑domain samples (N) supplied to the transform. With a 32‑bit register, the round‑off noise power is ( \sigma^2 = 1/(12·2^{2B}) ), effectively negligible for practical purposes. However, when the register width is reduced to 16 bits, the noise power rises by roughly 96 dB, leading to measurable amplitude and phase distortions. Moreover, the total round‑off noise scales approximately as ( \sigma^2_{\text{total}} ≈ N/(12·2^{2B}) ); thus, increasing N amplifies the noise, but the same increase also enables statistical averaging to suppress the variance by a factor of 1/M, where M is the number of averaged FFT outputs.

To mitigate the 16‑bit induced errors, the authors propose a practical compensation scheme based on oversampling within a short acquisition window followed by extensive averaging. In the frequency band of interest (≤ 2 kHz), a 4× oversampling factor combined with 64‑fold averaging reduces the phase error contributed by round‑off noise to below 0.1°, a level comparable to the ADC’s intrinsic phase uncertainty. The trade‑off between limiting ADC‑derived phase error and avoiding excessive averaging (which would increase processing time and memory requirements) is examined, and optimal parameters are identified for typical field deployments.

The appendix provides a rigorous derivation of the phase error caused by round‑off noise. By modeling the FFT output as a complex quantity ( X(k)=A(k)e^{j\phi(k)} ) perturbed by a small complex noise term ( e(k) ), a first‑order Taylor expansion yields ( \Delta\phi(k) ≈ \operatorname{Im}{e(k)}/A(k) ). This relationship shows that the phase error is inversely proportional to the signal amplitude, implying that low‑amplitude, high‑frequency components are most vulnerable to round‑off‑induced phase distortion.

In conclusion, while a 32‑bit FFT register would eliminate round‑off noise, the associated power consumption and hardware cost are prohibitive for portable RESPER systems. The study demonstrates that a 16‑bit implementation, when paired with judicious oversampling and averaging, can achieve measurement accuracies comparable to a higher‑precision design. This finding enables low‑cost, low‑power RESPER probes to retain high fidelity in both amplitude and phase, thereby broadening their applicability in geophysical surveys and related fields.

Comments & Academic Discussion

Loading comments...

Leave a Comment