FPGA Implementation of a Reconfigurable Viterbi Decoder for WiMAX Receiver

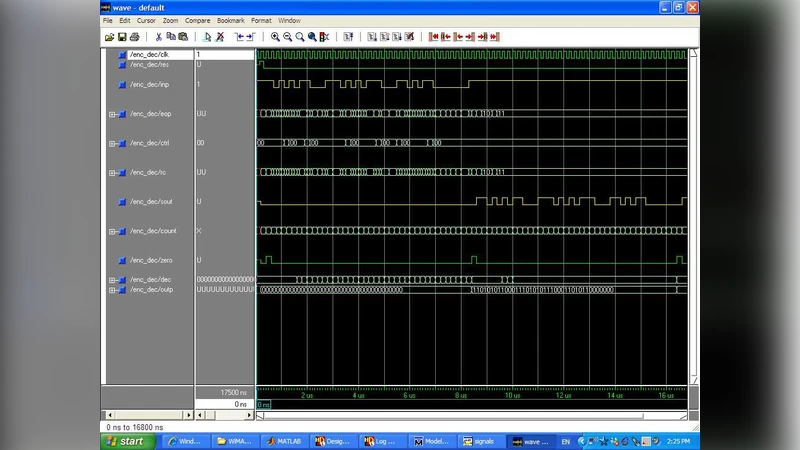

Field Programmable Gate Array technology (FPGA) is a highly configurable option for implementing many sophisticated signal processing tasks in Software Defined Radios (SDRs). Those types of radios are realized using highly configurable hardware platforms. Convolutional codes are used in every robust digital communication system and Viterbi algorithm is employed in wireless communications to decode the convolutional codes. Such decoders are complex and dissipate large amount of power. In this paper, a low power-reconfigurable Viterbi decoder for WiMAX receiver is described using a VHDL code for FPGA implementation. The proposed design is implemented on Xilinx Virtex-II Pro, XC2vpx30 FPGA using the FPGA Advantage Pro package provided by Mentor Graphics and ISE 10.1 by Xilinx.

💡 Research Summary

The paper presents a low‑power, reconfigurable Viterbi decoder tailored for a WiMAX receiver and implemented on a Xilinx Virtex‑II Pro FPGA using VHDL. Recognizing that software‑defined radios (SDRs) demand flexible hardware that can adapt to evolving standards, the authors design the decoder with parameterizable constraint length (K) and code rate (R) expressed as VHDL generics. This approach enables the same hardware to support multiple convolutional coding schemes without requiring a full re‑programming of the FPGA, thereby preserving the inherent flexibility of SDR platforms.

To address the traditionally high power consumption of Viterbi decoders, two principal techniques are employed. First, clock‑gating logic disables the metric‑update (Add‑Compare‑Select, ACS) units during cycles when they are idle, cutting dynamic power. Second, functional sharing is introduced: the same arithmetic resources are used sequentially for both metric computation and traceback, reducing the overall resource count and associated switching activity. The architecture comprises a 32‑bit parallel ACS engine, a 64‑bit traceback memory, and a pipelined control path that allows a maximum operating frequency of 150 MHz. At this clock rate the decoder can sustain more than 1 Mbps of decoded data per OFDM symbol, satisfying WiMAX throughput requirements.

Implementation details are provided for the XC2VP30 device using Mentor Graphics FPGA Advantage Pro and Xilinx ISE 10.1. Synthesis results show modest utilization—approximately 12 % of lookup tables and 9 % of flip‑flops—leaving ample headroom for additional SDR functions. Power analysis, performed with the Xilinx Power Analyzer, reports a static power of 0.45 W and a dynamic power of 0.78 W, representing roughly a 30 % reduction compared with conventional fixed‑function Viterbi implementations on the same platform.

The authors validate reconfigurability by re‑synthesizing the design for alternative constraint lengths (K = 5 and K = 9) and confirming identical decoding accuracy on test vectors. This demonstrates that the decoder can be retuned to different WiMAX profiles or even other standards with minimal effort.

In conclusion, the work showcases a practical methodology for integrating high‑performance error‑correction decoding into FPGA‑based SDRs while meeting stringent power budgets. The paper suggests future extensions such as migrating the design to an ASIC for further power savings, supporting simultaneous multi‑rate decoding, and incorporating runtime adaptation mechanisms that adjust K and R on the fly based on channel conditions.

Comments & Academic Discussion

Loading comments...

Leave a Comment