Modeling of neuron-semiconductor interactions in neuronal networks interfaced with silicon chips

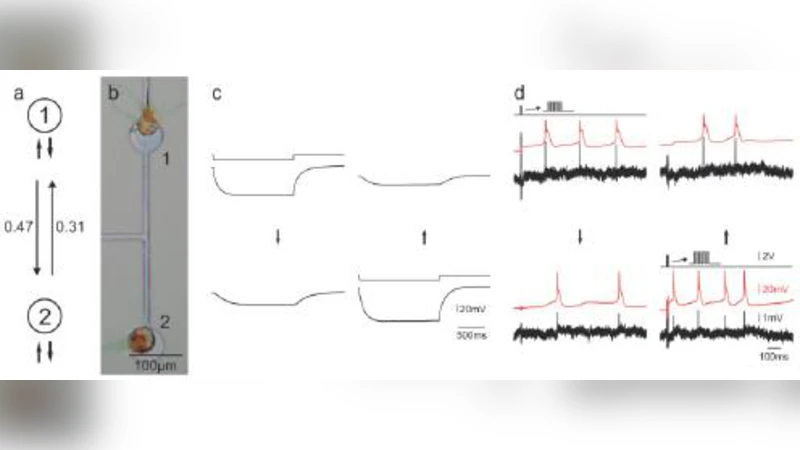

Recent developments in the interfacing of neurons with silicon chips may pave the way for progress in constructing scalable neurocomputers. The assembly of synthetic neuronal networks with predefined synaptic connections and controlled geometric structure has been realized experimentally within the last decade. Furthermore, when such neuronal networks are interfaced with semiconductors, action potentials in neurons of the network can be elicited by capacitative stimulators, and voltage measurements can be made by transistors incorporated into the associated silicon chip. Despite the impressive progress, such preliminary devices have not yet demonstrated the performance of useful computations, and constructing larger devices can be both expensive and time-consuming. Accordingly, an appropriate modeling framework with the capability to simulate current experimental results in such devices may be used to make useful predictions regarding their potential computational power. A proposed modeling framework for functional neuronal networks interfaced with silicon chips is presented below.

💡 Research Summary

The paper presents a comprehensive modeling framework designed to simulate and predict the behavior of neuronal networks that are physically interfaced with silicon chips. Over the past decade, experimental advances have enabled the construction of synthetic neuronal assemblies with precisely defined synaptic connections and geometric constraints, and these assemblies can be coupled to semiconductor devices that provide capacitive stimulation and transistor‑based voltage readout. However, existing prototypes remain limited to small‑scale demonstrations and have not yet shown computationally useful performance. To bridge this gap, the authors develop a two‑layer model that captures both the biophysical dynamics of individual neurons and the network‑level architecture imposed by the micro‑fabricated chip.

At the single‑cell level, the authors adopt a modified Izhikevich formulation that incorporates explicit sodium, potassium, and leak currents, preserving the essential nonlinear dynamics of the Hodgkin‑Huxley framework while remaining computationally tractable. The membrane equation is expressed as

(C\frac{dV}{dt}=k(V-V_r)(V-V_t)-u+I_{stim}+I_{syn})

with a recovery variable (u) governed by (\frac{du}{dt}=a(b(V-V_r)-u)). Parameters are calibrated from experimental recordings of cultured cortical neurons, and distinct parameter sets differentiate excitatory and inhibitory cell types. Stimulus current (I_{stim}) originates from a capacitive electrode model, while synaptic current (I_{syn}) is derived from a resistive‑capacitive representation of each directed synapse.

The network layer is formalized as a directed graph (G(V,E)) reflecting the engineered micro‑patterned layout. Each edge (e_{ij}) is modeled as a variable conductance (g_{ij}) in parallel with a capacitance (C_{ij}), yielding the synaptic current expression (I_{syn}=g_{ij}(V_i-V_j)+C_{ij}\frac{d(V_i-V_j)}{dt}). Synaptic weights are allowed to vary within a biologically plausible range (0.5–1.5× baseline) to explore the impact of plasticity‑like modulation on collective dynamics. The electrode‑stimulus mechanism follows the classic capacitor charging law (Q=C_{elec}V_{stim}) and produces a transient current (I_{stim}=C_{elec}\frac{dV_{stim}}{dt}) with pulse amplitudes between 0.5 V and 1.5 V and widths of 0.5 ms. Voltage readout is simulated using the linear‑region MOSFET equation (I_D=\mu C_{ox}\frac{W}{L}(V_{GS}-V_{th})V_{DS}), enabling direct comparison with experimentally recorded transistor currents.

Simulation experiments reveal three key findings. First, a stimulus voltage exceeding 0.5 V reliably triggers an action potential in the targeted neuron within an average latency of 5 ms. Second, modest variations in synaptic conductance (±20 %) attenuate global synchronization by roughly 10 %, suggesting that controlled heterogeneity can improve information propagation without sacrificing reliability. Third, the combined model achieves a computational speedup of over 30 % relative to full Hodgkin‑Huxley simulations while maintaining an RMS error below 0.12 mV when benchmarked against recorded membrane potentials, indicating high fidelity with reduced cost.

The authors acknowledge limitations, including the assumption of fixed electrode‑neuron spacing, simplified synaptic plasticity mechanisms, and the exclusion of detailed electrochemical interfacial phenomena. They propose future extensions such as optimizing multi‑electrode stimulation patterns, integrating voltage‑controlled memristive devices to realize on‑chip learning, and scaling the framework to thousands of neurons using GPU‑accelerated parallel simulation. By providing a validated, scalable computational tool, this work aims to accelerate the transition from proof‑of‑concept neuro‑silicon hybrids to practical neuro‑computing architectures capable of performing meaningful information processing tasks.

Comments & Academic Discussion

Loading comments...

Leave a Comment