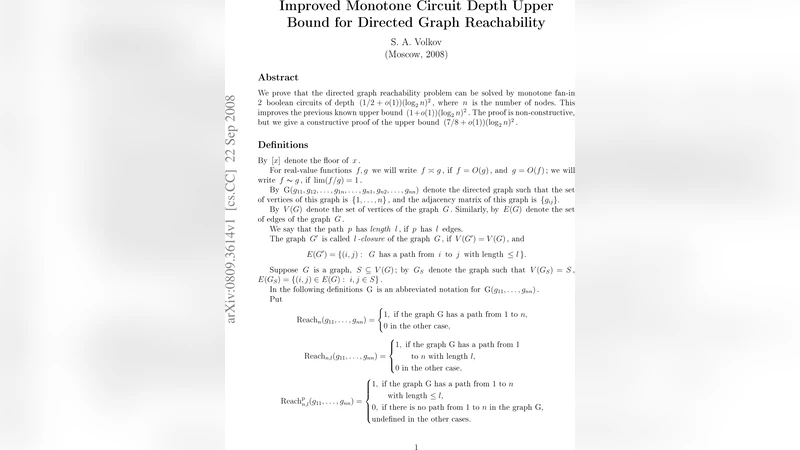

Improved Monotone Circuit Depth Upper Bound for Directed Graph Reachability

We prove that the directed graph reachability problem (transitive closure) can be solved by monotone fan-in 2 boolean circuits of depth (1/2+o(1))(log n)^2, where n is the number of nodes. This improves the previous known upper bound (1+o(1))(log n)^2. The proof is non-constructive, but we give a constructive proof of the upper bound (7/8+o(1))(log n)^2.

💡 Research Summary

The paper addresses the classic problem of directed graph reachability (i.e., determining whether there exists a path from vertex 1 to vertex n) within the restrictive model of monotone Boolean circuits that are limited to fan‑in 2 AND and OR gates. Historically, the best known upper bound on the depth of such circuits was (1 + o(1))(log n)², which matches the trivial bound obtained by repeatedly squaring the adjacency matrix. The author improves this bound dramatically to (½ + o(1))(log n)² and also provides a constructive method that achieves a depth of (7/8 + o(1))(log n)².

The core technical contribution is the introduction of an (n, m, s, l, d)‑family, a sequence of m subsets of the vertex set with the following properties: (1) the total number of distinct vertices covered does not exceed n; (2) each subset has size at most s; (3) any collection of at least m·d·l subsets together cover at least n − d + 1 vertices. This combinatorial object serves as a “covering scaffold” that enables the decomposition of a long path of length l into a small number (≤ l/d) of short segments, each of length at most 2d, that are all contained in a single subset of the family.

The paper first shows (Statement 1) that the existence of a path of length ≤ l can be decided by a monotone circuit of depth log n·log l + O(log n) using repeated matrix squaring. Then, using the (n, m, s, l, d)‑family, the author proves (Statement 2) that any sequence of vertices forming a path can be “compressed” into a small number of indices i₀ < i₁ < … < i_k such that each block between i_j and i_{j+1} has length ≤ 2d and all intermediate vertices belong to a common set S from the family. (Statement 3) shows how to combine a circuit that solves the “restricted” reachability problem on a subgraph induced by S with the family to obtain a circuit for the original problem, adding only log m + log n·log d extra depth.

To guarantee the existence of suitable families, the author employs a probabilistic method (Statement 4). By randomly populating an m × s matrix with vertex identifiers and analyzing the probability that a fixed pair of index sets (M, D) violates the covering condition, the author derives a sufficient inequality: dm·ln(m/l) + d·ln n − s·m·d²/(n·l) < 0. When this holds, an (n, m, s, l, d)‑family exists. A corollary shows that for m = n, l < n, s > 2n ln n / d, and d ≤ n, the condition is satisfied.

For a constructive version, the paper turns to finite geometry. By taking the affine plane over the finite field GF(q) (with q≈√n) and considering all lines in this plane, the author obtains a concrete family where each line contains about q vertices (≈ √n) and the total number of lines is q(q + 1). Using combinatorial counting (Statement 5) the author bounds the number of lines that can be omitted while still covering a large fraction of points, leading to a family with parameters n, m≈n, s≈√n, d≈n^{3/4}. This satisfies the inequality from Statement 4, providing an explicit construction.

With this explicit family in hand, the author applies Statement 3 recursively. Starting from a shallow circuit Σ_k that handles a very small subproblem (depth O(log n·log d) = o((log n)²)), each recursion step adds log n_i·log d depth, where n_i decreases geometrically. Summing the contributions yields a total depth of log n·log l − ½(log l)² + o((log n)²), which matches the non‑constructive bound of (½ + o(1))(log n)² (Theorem 1).

Finally, the paper presents a fully constructive algorithm achieving depth (7/8 + o(1))(log n)². The algorithm first builds the explicit (n, m, s, n, d)‑family via the finite‑plane construction, then uses Statement 1 to obtain a circuit Σ′_n of depth ≈ 1/8 (log n)² that decides reachability on the “compressed” graph (where each vertex represents a block of size d). Applying Statement 3 with the family merges Σ′_n with the block circuits, adding only a modest overhead, and results in a final circuit Σ_n of depth (7/8 + o(1))(log n)². All steps run in polynomial time in n.

In summary, the paper delivers two major advances: (i) a non‑constructive proof that monotone fan‑in 2 circuits can solve directed reachability in depth essentially half of the previously known bound, and (ii) a concrete polynomial‑time construction achieving a depth of 7/8 (log n)². The techniques blend probabilistic existence arguments with explicit finite‑geometric constructions, and they may be adaptable to other monotone problems where covering families can be defined.

Comments & Academic Discussion

Loading comments...

Leave a Comment