Enhancement of the number and array density of nozzles within an inkjet head chip is one of the keys to raise the printing speed and printing resolutions. However, traditional 2D architecture of driving circuits can not meet the requirement for high scanning speed and low data accessing points when nozzle numbers greater than 1000. This paper proposes a novel architecture of high-selection-speed three-dimensional data registration for inkjet applications. With the configuration of three-dimensional data registration, the number of data accessing points as well as the scanning lines can be greatly reduced for large array inkjet printheads with nozzles numbering more than 1000. This IC (Integrated Circuit) architecture involves three-dimensional multiplexing with the provision of a gating transistor for each ink firing resistor, where ink firing resistors are triggered only by the selection of their associated gating transistors. Three signals: selection (S), address (A), and power supply (P), are employed together to activate a nozzle for droplet ejection. The smart printhead controller has been designed by a 0.35 um CMOS process with a total circuit area, 2500 x 500 microm2, which is 80% of the cirucuit area by 2D configuration for 1000 nozzles. Experiment results demonstrate the functionality of the fabricated IC in operation, signal transmission and a potential to control more than 1000 nozzles with only 31 data access points and reduced 30% scanning time.

Deep Dive into Reduced 30% scanning time 3D multiplexer integrated circuit applied to large array format 20KHZ frequency inkjet print heads.

Enhancement of the number and array density of nozzles within an inkjet head chip is one of the keys to raise the printing speed and printing resolutions. However, traditional 2D architecture of driving circuits can not meet the requirement for high scanning speed and low data accessing points when nozzle numbers greater than 1000. This paper proposes a novel architecture of high-selection-speed three-dimensional data registration for inkjet applications. With the configuration of three-dimensional data registration, the number of data accessing points as well as the scanning lines can be greatly reduced for large array inkjet printheads with nozzles numbering more than 1000. This IC (Integrated Circuit) architecture involves three-dimensional multiplexing with the provision of a gating transistor for each ink firing resistor, where ink firing resistors are triggered only by the selection of their associated gating transistors. Three signals: selection (S), address (A), and power suppl

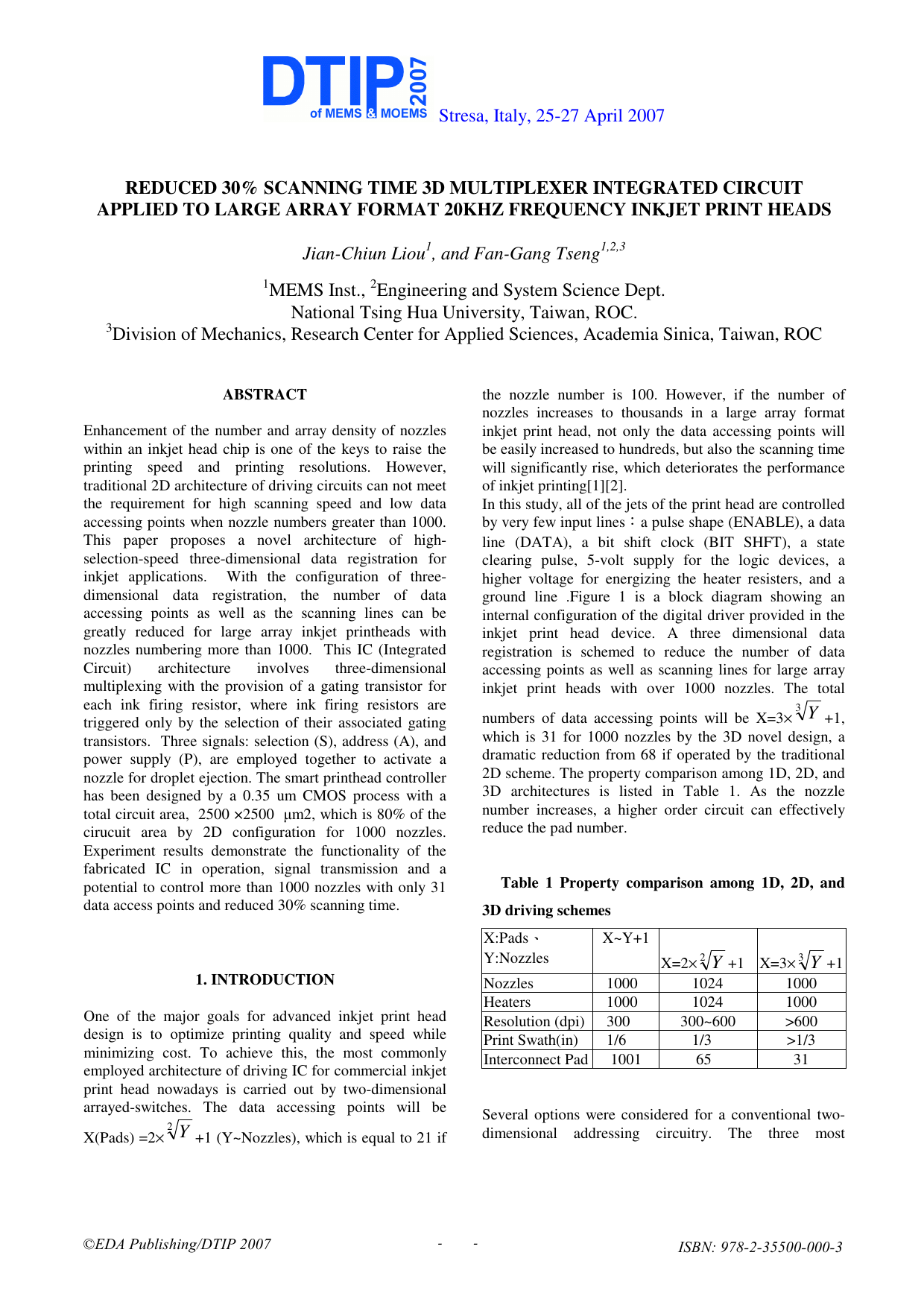

One of the major goals for advanced inkjet print head design is to optimize printing quality and speed while minimizing cost. To achieve this, the most commonly employed architecture of driving IC for commercial inkjet print head nowadays is carried out by two-dimensional arrayed-switches. The data accessing points will be X(Pads) =2× 2 Y +1 (Y~Nozzles), which is equal to 21 if the nozzle number is 100. However, if the number of nozzles increases to thousands in a large array format inkjet print head, not only the data accessing points will be easily increased to hundreds, but also the scanning time will significantly rise, which deteriorates the performance of inkjet printing [1] [2]. In this study, all of the jets of the print head are controlled by very few input lines a pulse shape (ENABLE), a data line (DATA), a bit shift clock (BIT SHFT), a state clearing pulse, 5-volt supply for the logic devices, a higher voltage for energizing the heater resisters, and a ground line .Figure 1 is a block diagram showing an internal configuration of the digital driver provided in the inkjet print head device. A three dimensional data registration is schemed to reduce the number of data accessing points as well as scanning lines for large array inkjet print heads with over 1000 nozzles. The total numbers of data accessing points will be X=3× 3 Y +1, which is 31 for 1000 nozzles by the 3D novel design, a dramatic reduction from 68 if operated by the traditional 2D scheme. The property comparison among 1D, 2D, and 3D architectures is listed in Table 1. As the nozzle number increases, a higher order circuit can effectively reduce the pad number. When the row and column connected with the resistor cell are applied a positive voltage, the transistor will conduct and generate a current flow through the resistor. Then the resistor will heat the ink, generating bubbles to spray the ink droplets.

In the proposed novel 3D design, different from the 2D one, as shown in Figure 1, the digital driver includes a clock-control circuit, a serial/parallel-conversion circuit , a latch circuit , a level shifter, a D/A converter comprised of a decoder, and an output buffer comprised of an operation amplifier . The received inkjet data needs to be converted into data at an optimal transfer rate (frequency) in order to conform to the inkjet characteristics. To this end, the clock-control circuit divides the 8-bit inkjet signals supplied to the data driver, with an aim of lowing the operation frequency. The serial/parallel-conversion circuit converts serial signals of a plurality of channels into parallel signals, and supplies the parallel signals to the latch circuit. The latch circuit temporarily stores therein the received parallel signals, and supplies same to the level shifter and the D/A converter at predetermined timings. The level shifter converts a logic level ranging approximately from 3.5 V to 5 V into a inkjet voltage level that ranges from 7.5V to 8.5V for various heater resistors as a result of variation processing conditions. The control circuit is divided into two parts: the pass-gate device (for signal path) and the power device (for power path), as shown in Figure 2 .The pass gate device is controlled by A selection and S selection, while the power line is controlled by P selection. To activate one heater, all P, A, and S selections are required to be turned on at once. For example, to turn on the heater 1, P1, A1 and S1 need to be set high at the same time. The scanning time is reduced up to 30% (The scanning speed is also increased by 3 times) thanks to the great reduction of lines for 3D scanning, rather than 2D scanning. Figure 3 shows the numbers of the required connection pads for 1D, 2D and 3D control circuit. As the nozzle number increases, the required connection pads are increasing but with different rates. The 1D case increases most rapidly while the 3D one increases at the slowest pace. There are two important intersections in the three curves, which are, the one with the nozzle number of 10 and the other, 30. When the nozzle number is much larger than 100, the 3D architecture can dramatically reduce the pad number in tens.

Figure 4 is the input-output relationship of the ASIC we observe with the Logic Analysis equipment. The output signal is matched to the designed function .An input signals waveform concept can be used to TIJ to address each jet . The depicted integrated circuit TIJ transducer array serves 1000 jets and includes data interfacing , jet addressing. The desired signal for S selections and A selections can be pre-registered and latched in the circuit for one time writing. Combining this scheme with the P selection control, simultaneous 3D driving can be realized. The enhancement will be even sounder in larger nozzle arrays. Figure 5 illustrates the transient simulation of the input and output signal of the level shift device [3][4] [5]. The signal demonstrates that not only the switch speed is h

…(Full text truncated)…

This content is AI-processed based on ArXiv data.