고수준 합성에서 에이전트 공장 일반 목적 코딩 에이전트의 최적화 한계

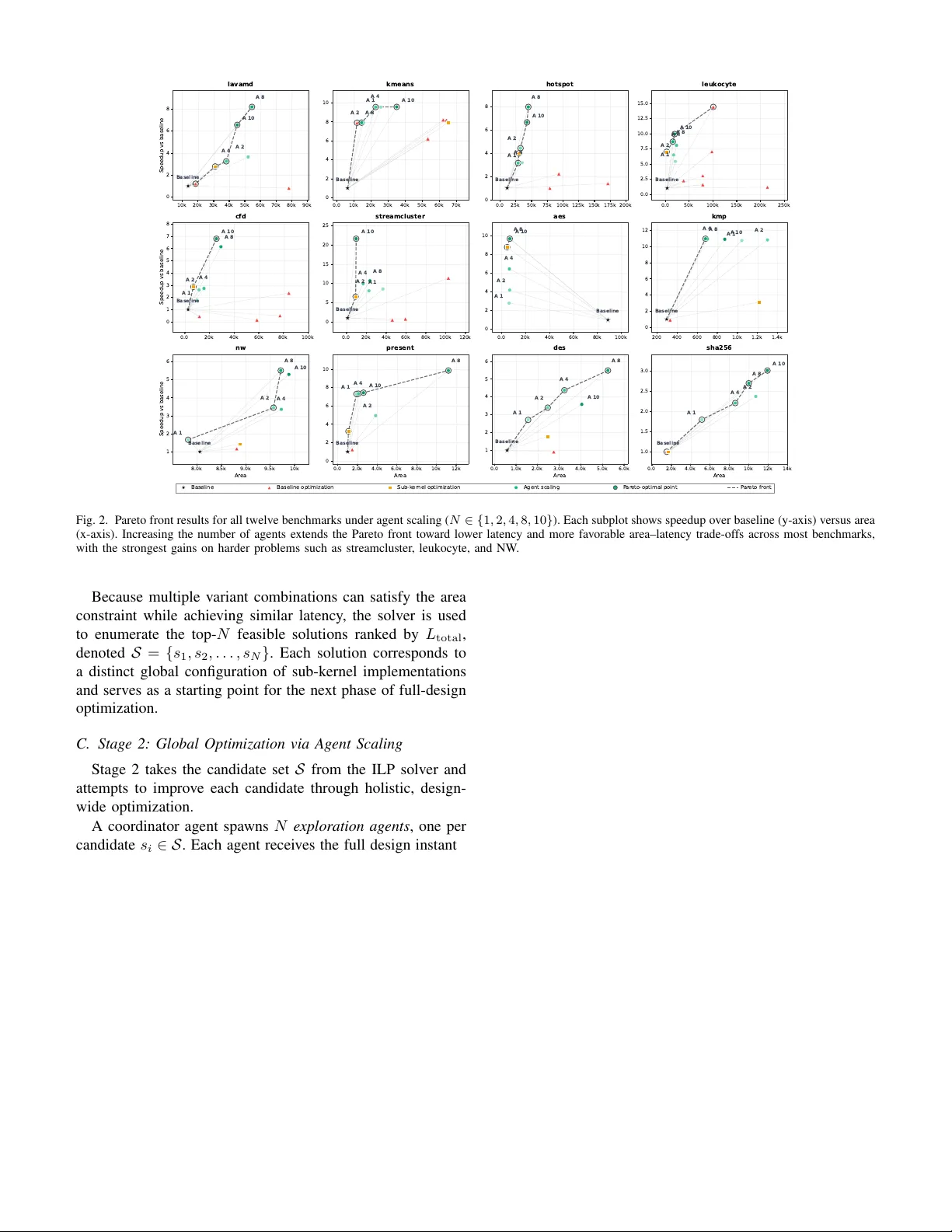

본 논문은 하드웨어 전용 학습 없이 일반 목적 코딩 에이전트를 활용해 고수준 합성(HLS) 설계를 최적화하는 방법을 제안한다. 두 단계 파이프라인인 에이전트 공장은 먼저 서브 커널을 분해·최적화하고 ILP로 전역 구성을 선택한 뒤, 상위 ILP 후보들을 여러 전문가 에이전트가 동시에 탐색해 pragma 재조합·루프 융합·메모리 재구성을 수행한다. 12개의 벤치마크에 대해 1~10개의 에이전트를 사용했을 때 평균 8.27배, 최악의 경우 20배 …

저자: Abhishek Bh, waldar, Mihir Choudhury

본 논문은 고수준 합성(HLS) 설계에서 하드웨어 전용 학습 없이 일반 목적 코딩 에이전트를 활용해 최적화를 수행할 수 있는 가능성을 실증한다. 연구진은 ‘에이전트 공장’이라 명명한 두 단계 파이프라인을 설계했으며, 첫 단계에서는 입력 프로그램을 함수 호출 그래프(G)로 분해하고, 각 서브 함수에 대해 7가지 사전 정의된 변형을 생성한다. 변형은 보수적 pragma 적용, 파이프라인 II 조정, 언롤, 배열 파티션, 인라인, 그리고 수식 변환 등을 포함한다. 각 변형은 기능 검증 후 AMD Vitis HLS를 통해 지연(L)과 면적(A) 특성을 측정하고, 실패한 경우는 폐기한다. 이후 전역 면적 제한을 만족하면서 전체 지연을 최소화하는 정수선형계획(ILP) 문제를 풀어, 서브 커널 조합의 최적 후보 N개를 선정한다.

두 번째 단계에서는 ILP에서 추출한 N개의 후보 설계를 각각 초기 상태로 하는 N개의 탐색 에이전트를 동시에 실행한다. 각 에이전트는 pragma 재조합, 루프 재배열·융합·인라인, 메모리 재구성, 연산 재작성 등 네 가지 전역 최적화 경로를 순차적으로 적용한다. 변형된 설계는 다시 합성·검증 과정을 거쳐 지연·면적을 기록하고, 예산을 초과하지 않는 경우 최적 설계 후보로 유지한다. 최종 결과는 모든 에이전트가 탐색한 설계 중 지연이 최소이며 면적 제한을 만족하는 설계 D*이다.

실험은 HLS‑Eval와 Rodinia‑HLS에서 선정한 12개의 커널에 대해 수행했으며, Claude Code(Opus 4.5/4.6)와 AMD Vitis HLS를 사용했다. 에이전트 수를 1, 2, 4, 8, 10으로 변화시켰을 때 평균 속도 향상은 1배에서 8.27배까지 증가했으며, 특히 복잡한 워크로드인 streamcluster는 20배, kmeans는 약 10배의 가속을 보였다. 에이전트들은 기존 전문가가 적용하는 ARRAY_PARTITION, PIPELINE 의존성 해결, 루프 언롤 등 알려진 최적화 패턴을 자동으로 재현했으며, 때때로 ILP 상위 후보가 아닌 설계에서도 최고의 성능을 찾아 전역 탐색의 가치를 입증했다. 그러나 단순 파이프라인 중심의 커널에서는 에이전트 수 증가에 따른 성능 향상이 포화되는 등 한계도 확인되었다. 논문은 이러한 결과를 바탕으로 일반 목적 LLM 에이전트를 하드웨어 최적화에 적용하는 초기 베이스라인을 제시하고, 향후 다양한 벤치마크, 모델, 툴체인으로 확장할 필요성을 강조한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기