초저지연 방사선 내구 FPGA에서 머신러닝 구현: hls4ml 기반 자동 압축

본 논문은 LHCb Upgrade II의 PicoCal 칼로미터를 대상으로 32채널 타이밍 파형을 2차원 잠재공간으로 압축하는 경량 자동인코더를 설계하고, 10비트 가중치 양자화를 적용해 성능 손실을 최소화하였다. 또한 Microchip PolarFire 방사선 내구 FPGA용 hls4ml 백엔드를 새롭게 구현하여 자동 HLS 변환을 가능하게 했으며, 합성 결과 25 ns 이하의 레이턴시와 제한된 리소스 사용을 확인했다.

저자: Katya Govorkova, Julian Garcia Pardinas, Vladimir Loncar

본 논문은 LHCb Upgrade II 프로젝트의 PicoCal 전자칼로미터를 대상으로, 방사선 내구 FPGA인 Microchip PolarFire에서 초저지연 머신러닝(ML) 모델을 구현하는 전 과정을 상세히 기술한다. 서론에서는 HL‑LHC 시대에 데이터량 폭증과 높은 펨토초 수준의 타이밍 요구가 결합되어, 디지털 신호를 현장(Edge)에서 실시간으로 압축·처리해야 하는 필요성을 강조한다. 기존 ASIC 기반 솔루션은 개발 주기와 비용이 크고, SRAM‑기반 FPGA는 SEU에 취약해 TMR이 필수적인 반면, 플래시 기반 PolarFire는 비휘발성 구성 메모리로 SEU에 강인해 방사선 환경에 적합하다는 점을 제시한다.

관련 연구에서는 자동인코더를 이용한 데이터 압축 및 이상 탐지, 그리고 hls4ml을 활용한 FPGA 배포 흐름을 검토한다. 그러나 기존 hls4ml은 Xilinx·Intel 전용이며, 방사선 내구 FPGA에 대한 지원이 없었다는 점을 문제점으로 지적한다.

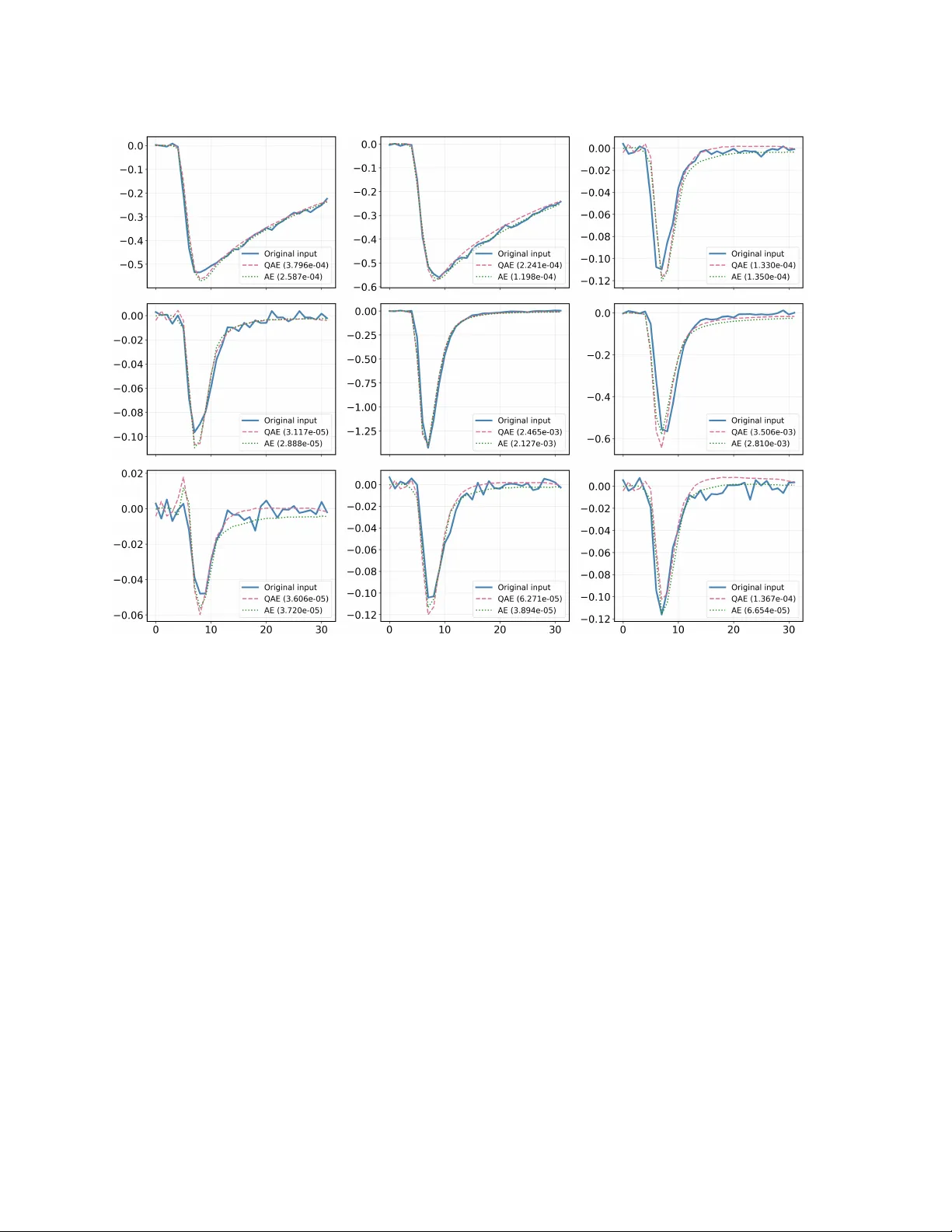

제안된 자동인코더는 32개의 16‑bit 샘플을 입력으로 받아, 단일 Dense 레이어와 ReLU 활성화를 통해 2‑차원 잠재공간으로 직접 매핑한다. 디코더는 학습 단계에서만 사용되며, 대칭 구조와 선형 활성화로 원본 파형을 복원한다. 이 구조는 파라미터 수를 최소화하면서도 파형의 상승 시간, 피크 위치 등 핵심 물리 정보를 보존한다. 학습 데이터는 Geant4 기반 Monte‑Carlo 시뮬레이션으로 생성했으며, 신호와 배경(펄스 중첩) 데이터를 결합해 실제 런‑5 조건을 재현하였다. 모델은 MSE 손실함수와 Adam 옵티마이저로 200 epoch 학습했으며, 검증 단계에서 재구성 오차가 0.3 % 이하로 수렴했다.

양자화 연구에서는 32‑bit 부동소수점 가중치를 10‑bit 정수형으로 축소하는 과정을 단계별로 수행했다. 각 단계마다 양자화 인식 훈련(quantization‑aware training)을 적용해 손실을 보정했으며, 10‑bit 양자화 후에도 물리적 성능(에너지 분해능, 타이밍 정확도)이 거의 변하지 않음을 확인했다. 이는 FPGA 내부에서 고정소수점 연산만으로도 충분히 정확한 추론이 가능함을 의미한다.

핵심 공헌은 hls4ml 백엔드의 신규 구현이다. 저자들은 Microchip SmartHLS 컴파일러를 목표로, 모델 정의를 JSON 형태로 받아 C++ HLS 코드와 Makefile을 자동 생성하는 파이프라인을 구축했다. 이 백엔드는 레이어별 파이프라인 지연, 루프 언롤링, 자원 공유 옵션을 자동 설정하고, PolarFire 전용 IP 코어와 인터페이스를 제공한다. 이를 통해 TensorFlow/Keras 모델을 몇 분 안에 RTL 수준의 설계로 변환할 수 있다.

합성 결과는 PolarFire MPFS‑SC025 디바이스에서 25 ns(40 MHz 클럭 기준 4 사이클) 이하의 레이턴시를 달성했으며, 사용된 LUT 8 %, DSP 6 %, BRAM 5 % 수준으로 전체 자원 대비 낮은 비율을 차지했다. 또한, 설계는 FPGA 내부 보호 로직 영역에 배치돼 방사선 내구성을 확보했다. 다중 채널(8채널 동시 처리) 시나리오에서도 파이프라인 복제와 메모리 대역폭 관리가 가능하도록 설계가 확장 가능함을 제시한다.

논의에서는 방사선 테스트 미실시, 2‑차원 잠재공간의 일반화 한계, 다중 채널 확장 시 발생할 수 있는 전력·열 관리 문제 등을 언급하며, 향후 실제 실험실 프로토타입 제작 및 방사선 시험, 더 높은 차원의 잠재공간 탐색, 그리고 하드웨어‑소프트웨어 공동 최적화 연구가 필요함을 제안한다. 결론적으로, 경량 자동인코더, 하드웨어 친화적 양자화, 그리고 hls4ml 기반 자동 HLS 변환이라는 세 축을 성공적으로 결합함으로써, 방사선 내구 FPGA에서 초저지연 ML 적용을 실현하고, 향후 고에너지 물리 실험의 온‑디텍터 데이터 처리 패러다임을 크게 전환시킬 수 있음을 입증한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기