신경망 기반 자기 간섭 제거의 하드웨어 구현

본 연구는 동일 주파수 대역에서 송수신이 동시에 이루어지는 인밴드 풀듀플렉스 시스템의 핵심 문제인 자기 간섭을 해결하기 위해, 신경망 기반 비선형 디지털 자기 간섭 제거기의 하드웨어 아키텍처를 제안합니다. 기존 다항식 기반 제거기와의 비교를 통해, 심층 신경망 제거기가 최대 2.1배 향상된 하드웨어 효율과 2배 향상된 에너지 효율을 달성하며, 성능과 구현 복잡성 측면 모두에서 우수함을 입증합니다.

저자: Yann Kurzo, Andreas Toftegaard Kristensen, Andreas Burg

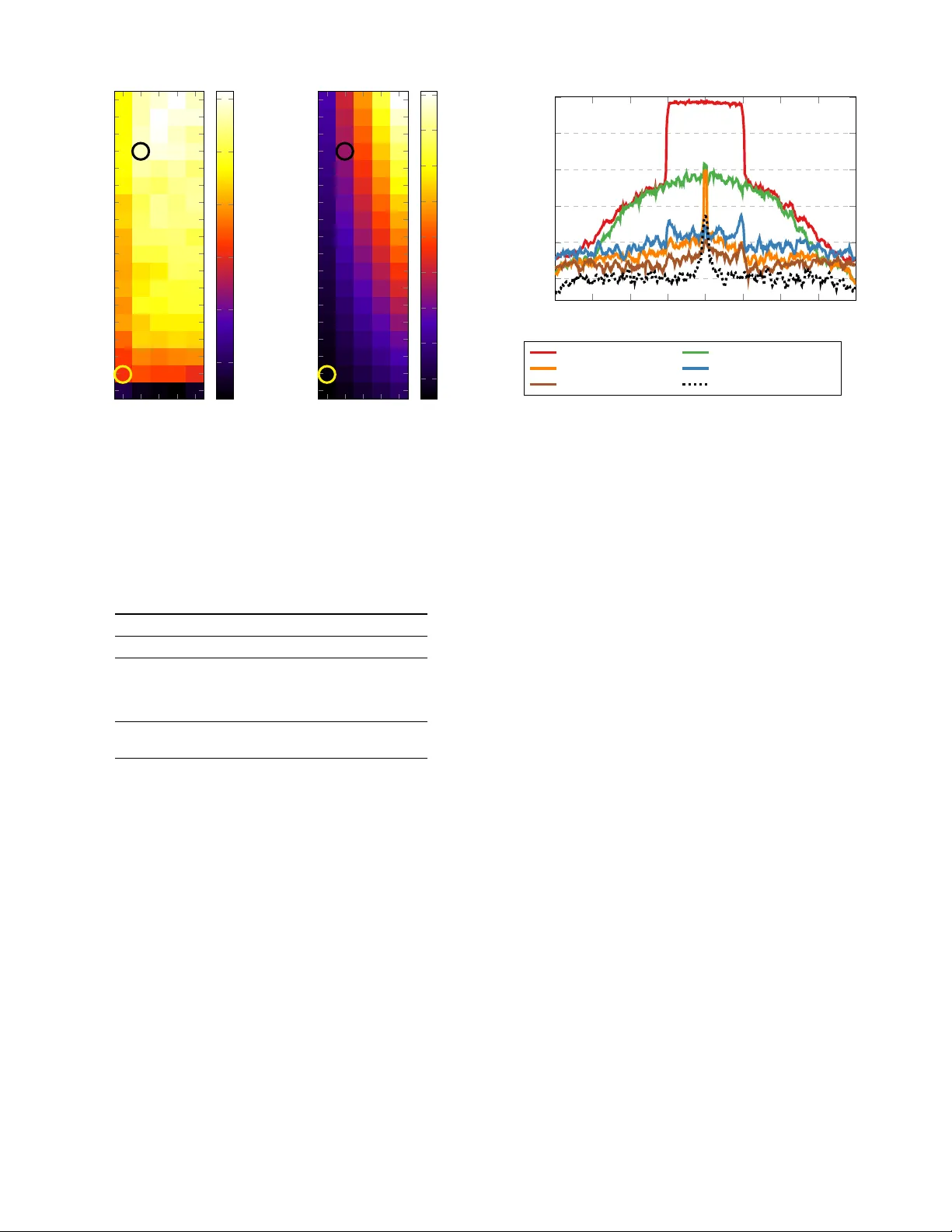

이 논문은 인밴드 풀듀플렉스 통신 시스템에서 발생하는 강력한 자기 간섭 문제를 해결하기 위한 디지털 신호 처리기의 하드웨어 구현에 관한 연구입니다. 자기 간섭은 수신기에 전달되는 송신 신호로, 시스템 성능을 크게 저하시키며, 특히 전력 증폭기, IQ 변조기 등의 비선형 특성으로 인해 선형 필터링만으로는 완전히 제거하기 어렵습니다. 저자는 기존의 표준 해결책인 고차 다항식 기반 모델과 대안으로 떠오르는 신경망 기반 모델을 실제 하드웨어(FPGA 및 ASIC)로 구현하고, 그 성능, 처리량, 면적, 에너지 효율을 체계적으로 비교 평가합니다.

논문은 먼저 풀듀플렉스 트랜시버 구조와 자기 간섭 신호의 수학적 모델을 설명합니다. 다항식 모델은 비선형성 차수(P)와 메모리 길이(L)에 따라 복잡도가 급격히 증가하는 병렬 해머스타인 구조를 따릅니다. 신경망 모델은 '보편 근사 정리'에 기반하여, 선형 취소기로 먼저 주된 선형 성분을 제거한 후, 잔여 비선형 성분만을 신경망이 예측하는 하이브리드 방식을 채택합니다. 이는 학습의 어려움을 완화하고 NN의 복잡도를 줄이는 효과적인 전략입니다.

핵심 기여는 두 가지 하드웨어 아키텍처의 상세 설계입니다. 신경망 가속기 아키텍처는 높은 처리량 요구사항을 만족시키기 위해 완전히 파이프라인화된 구조를 제안하며, 은닉층의 노드 계산을 높은 병렬도로 수행합니다. 비교 대상인 다항식 가속기는 모든 기저 함수(예: x, x|x|^2, x*|x|^2 등)를 생성하고 이에 대한 복소수 필터 계수를 곱하는 연산을 효율적으로 매핑합니다. 구현 결과, 28nm CMOS 공정에서의 ASIC 구현에서 심층 신경망(은닉층 4개) 제거기는 312.8 Msamples/s/mm^2의 면적 효율과 0.9 nJ/sample의 에너지 효율을 달성하여, 동일 조건의 다항식 제거기 대비 각각 2.1배, 2배 우수한 성능을 보였습니다. 또한, 동일한 칩 면적 대비 최대 7dB 더 우수한 간섭 제거 성능을 제공할 수 있음을 입증하며, 신경망 접근법이 알고리즘 성능뿐만 아니라 실질적인 하드웨어 비용 절감과 전력 효율 개선에 매우 유용함을 강력하게 뒷받침합니다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기