펄스 폭 변조 기반 초저전력 아날로그 뉴럴 네트워크 프로세서

본 논문은 펄스 폭 변조(PWM) 방식을 활용한 시간 영역 아날로그 가중합 계산 모델(TACT-PWM)을 제안한다. 이 모델은 멀티레이어 피드포워드 네트워크를 포함한 다양한 구조에 적용 가능하며, 연산 증폭기 없이 동작하는 초저전력 VLSI 회로로 구현된다. 250nm 공정으로 제작된 바이너리 가중치(BinaryConnect) 검증 칩은 300 TOPS/W의 탁월한 에너지 효율을 달성했으며, 최신 공정 적용 시 1,000 TOPS/W 이상의 효…

저자: Masatoshi Yamaguchi, Goki Iwamoto, Hakaru Tamukoh

본 논문은 펄스 폭 변조(PWM) 신호를 활용한 새로운 시간 영역 아날로그 가중합 계산 모델(TACT-PWM)과 이를 구현한 초저전력 VLSI 신경망 프로세서를 제안한다. 기존의 전압/전류 모드 아날로그 회로와 달리, 이 방식은 커패시터 충전/방전의 과도 상태 동작을 계산에 이용하며, 고전류를 필요로 하는 연산 증폭기를 사용하지 않아 극히 낮은 전력 소모가 가능하다. 대신 기가옴 급의 고저항 소자가 필요하며, 이는 MOSFET을 서브스레숄드 영역에서 동작시켜 구현했다.

논문은 먼저 기본 계산 모델을 수학적으로 정의한다. 다수의 스위치드 전류원(SCS)이 PWM 입력 신호에 따라 커패시터를 충전하면, 축적된 전하량(Q)이 각 입력 펄스 폭(W_i)과 전류(I_i)의 곱의 합(가중합)이 된다. 이어서 뉴런 회로에서는 이 커패시터 전압(V_mac)을 기준으로, 다른 고정 전류원으로 커패시터를 재충전하여 비교기 문턱전압에 도달하는 시간을 측정함으로써, 결과를 다시 PWM 폭(W_out)으로 변환출력한다. 양수/음수 가중치 계산은 별도의 라인에서 수행된 후 최종적으로 차이를 구하며, ReLU 함수는 간단한 논리 회로로 구현된다.

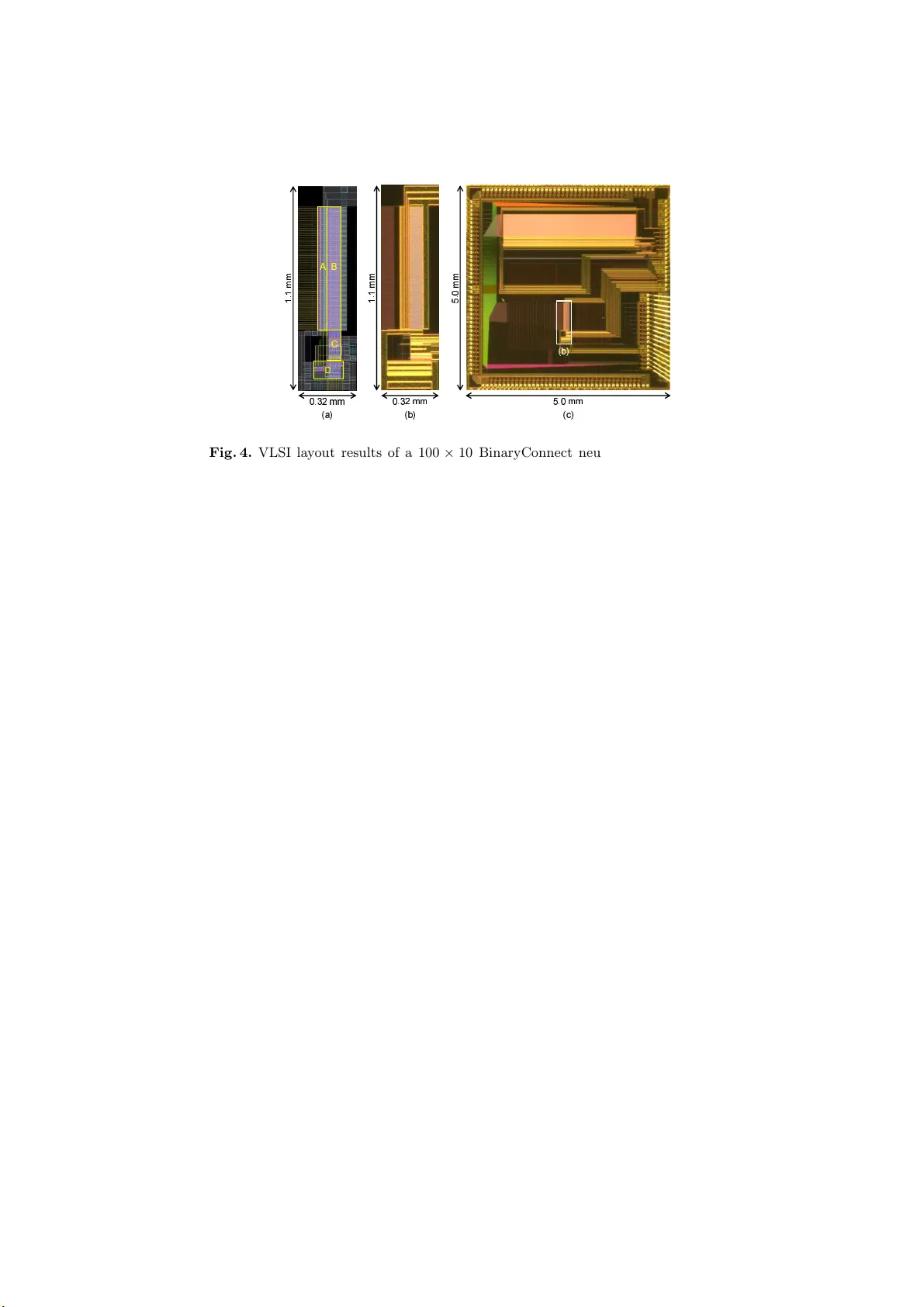

이 모델을 검증하기 위해 저자들은 BinaryConnect(아날로그 입력, 바이너리 가중치) 모델을 구현하는 CMOS 칩을 TSMC 250nm 공정으로 설계 및 제작했다. 신경망 구조는 100개의 시냅스와 10개의 뉴런으로 구성된다. 시냅스 부분은 SRAM 셀을 변형한 BSU(Binary Synapse Unit) 배열로, 플립플롭으로 바이너리 가중치를 저장하고 서브스레숄드 pMOSFET을 통해 해당 가중치에 맞는 미세 전류를 덴드라이트 라인으로 공급한다. 측정 결과, 단일 뉴런에서의 가중합 계산은 양호한 선형성을 보였으나, MOSFET 특성 변동으로 인한 약 ±1%의 정밀도 한계와 오프셋이 관찰되었다. ReLU 함수를 포함한 종단간 계산에서는 평균 1.5%의 오차를 보였다.

가장 주목할 만한 성과는 에너지 효율이다. 측정 조건에서 칩은 300 TOPS/W(테라-연산/초/와트)의 효율을 기록했으며, 이는 최신 디지털 AI 프로세서 대비 한 자릿수 이상 우수한 성능이다. 특히 이 결과는 상대적으로 낙후된 250nm 공정에서 얻어진 것임을 강조한다. 논문은 최신 공정(예: 7nm 이하)을 적용하여 기생 커패시턴스를 줄인다면 1,000 TOPS/W(1 POPS/W)를 넘는 효율을 달성할 수 있을 것으로 전망한다. 결론적으로, 이 TACT-PWM 접근법은 뇌 수준에 근접한 에너지 효율의 신경망 하드웨어 구현을 위한 유망한 길을 제시하지만, 실용적인 정밀도를 보장하기 위해서는 FeFET와 같은 변동성이 적은 아날로그 메모리 소자의 개발이 선행되어야 함을 역설한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기