병렬 이미지 처리용 파이프라인 매핑의 이중 기준 최적화

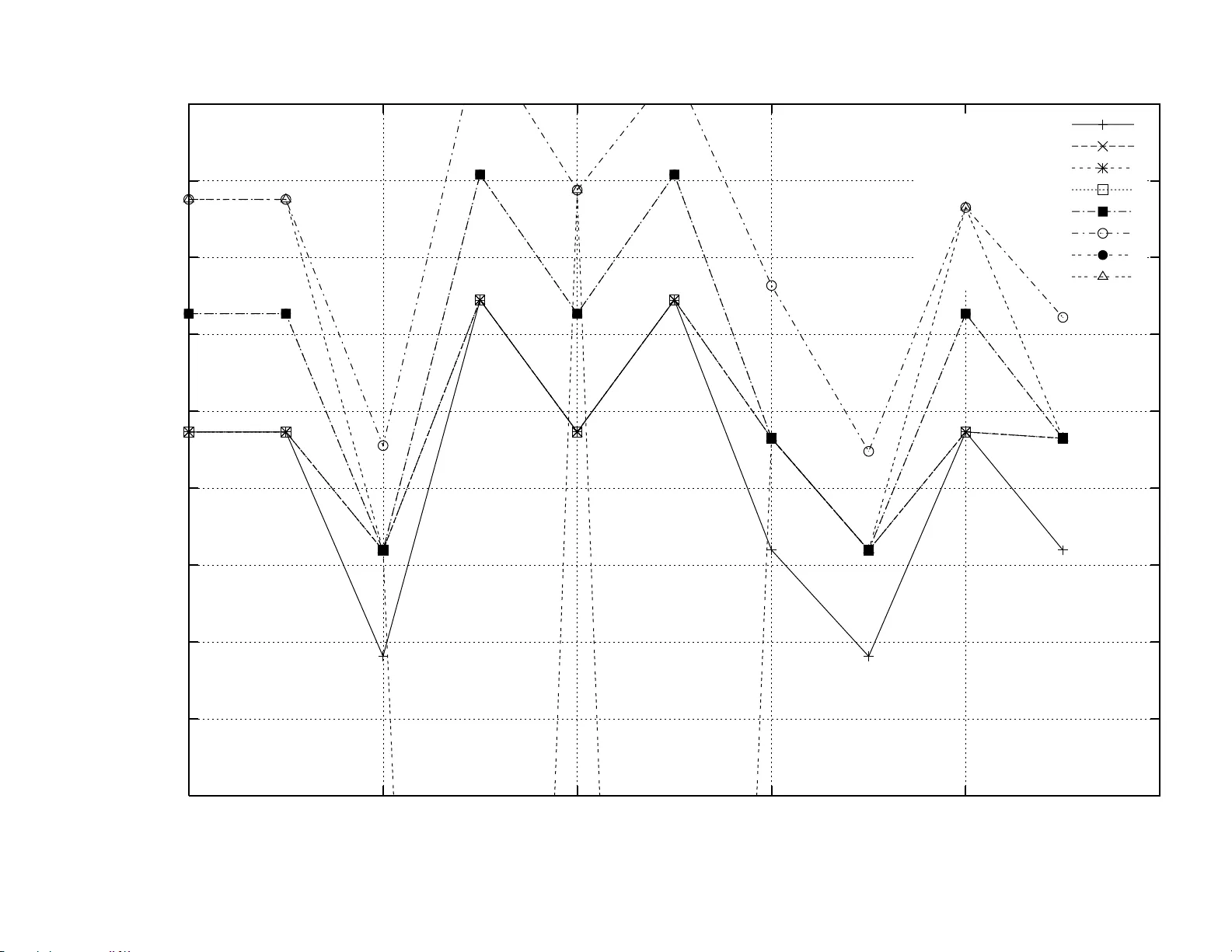

본 논문은 JPEG 인코딩 파이프라인을 병렬 플랫폼에 매핑할 때, 처리량(주기)과 지연시간(레턴시)이라는 두 상충 목표를 동시에 최적화하는 문제를 다룬다. 문제의 NP‑완전성을 보이고, 완전 탐색 대신 다항식 시간 휴리스틱 6종(H1‑H6)을 설계·평가한다. 또한 이종 프로세서와 통신 비용을 고려한 정수 선형계획(ILP) 모델을 제시한다. 실험을 통해 휴리스틱이 실제 환경에서 좋은 근사해를 제공함을 확인한다.

저자: Anne Benoit (INRIA Rh^one-Alpes, LIP), Harald Kosch

**1. 서론**

병렬 플랫폼에 워크플로우를 매핑하는 문제는 이미 오래전부터 연구되어 왔지만, 이질적인 프로세서와 복잡한 통신 구조를 가진 현대 시스템에서는 여전히 도전 과제로 남아 있다. 저자들은 특히 파이프라인 형태의 워크플로우에 초점을 맞추어, JPEG 인코딩 파이프라인을 사례 연구로 선택한다. JPEG 인코딩은 7개의 순차적 단계로 구성되며, 각 단계는 입력 데이터 크기와 연산량이 명확히 정의돼 있어 모델링이 용이하다.

**2. JPEG 인코딩 파이프라인**

- **Stage 1: 스케일링** – 이미지 크기를 8×8 혹은 16×16 블록에 맞게 조정한다.

- **Stage 2: 색공간 변환** – RGB → YUV 변환을 수행한다.

- **Stage 3: 서브샘플링** – 인간 시각 특성을 이용해 색채 정보를 감소시킨다(옵션).

- **Stage 4: MCU 생성** – 8×8 픽셀 블록을 최소 코딩 유닛(MCU)으로 저장한다.

- **Stage 5: FDCT** – 각 MCU에 대해 2‑D 빠른 코사인 변환을 수행한다.

- **Stage 6: 양자화** – 변환 계수를 양자화하여 불필요한 고주파 성분을 제거한다.

- **Stage 7: 엔트로피 코딩** – 수정된 Huffman 코드를 이용해 압축한다.

각 단계는 입력 크기 δₖ₋₁, 출력 크기 δₖ, 연산량 wₖ 로 표현된다.

**3. 목표 플랫폼 모델**

플랫폼은 p개의 프로세서 Pᵤ (1 ≤ u ≤ p) 로 구성되며, 완전 연결된 가상 클리크 형태이다. 프로세서 속도 sᵤ와 링크 대역폭 bᵤ,ᵥ가 정의되고, 연산 X는 X/sᵤ 시간, 통신 X는 X/bᵤ,ᵥ 시간으로 모델링한다. 통신 충돌은 “one‑port” 모델을 적용해 하나의 프로세서가 동시에 하나의 링크만 사용할 수 있도록 제한한다.

**4. 이중 기준 인터벌 매핑 문제 정의**

스테이지 집합

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기